0 引 言

雷达是利用电磁信号探测并定位目标的复杂电子设备,早在一战期间,英国人第一次把雷达试验系统用到了战场上,用于搜索和警戒来袭的德国飞机;二战期间,雷达的功能、技术能力和水平得到了快速发展,在战场上担负越来越重要的角色。用于军事用途的早期的雷达大多为地面设备,受器件水平和处理能力的限制,其功率孔径和设备量通常都较为庞大。从20世纪60年代开始,随着微电子和计算机技术的飞速发展,雷达性能不断提升,形态不断发生变化,应用场景从军用领域向民用领域渗透,雷达技术被认为是一项“古老而不断演进”的技术[1]。目前,在军用领域的无人机、无人战车、手持感知设备等小型化作战装备、精确攻击武器导引头设备等在战场中担负着越来越重要的作用;在民用领域,智能驾驶、生命探测、安检成像、手势识别等产业快速发展,这些场景都对雷达小型化、低功耗、低成本等提出了更加苛刻的需求。微电子和半导体技术的快速发展为雷达小型化提供了新的契机,先进集成电路芯片和先进封装技术使得雷达系统集成度越来越高,体积、功耗和成本持续降低。目前,高度集成的小型化雷达甚至芯片化雷达在无人机[2]、智能汽车[3-4]、安检成像[5-6]、手势识别[7]等民用领域已经获得突破和应用。

地面远程监视雷达为了获得好的探测威力,通常采用较大的雷达功率孔径积,美国的THAAD系统配置的AN/TPY-2雷达系统,天线阵面孔径为9.2 m2,安装有3万个天线单元,雷达系统重量超过30 t。由于受飞机平台重量、空间和功耗的限制,机载雷达规模要小很多,美国早期的AN/AWG-9机载火控雷达,直径0.91 m,雷达重量612 kg,是当时最大的机载火控雷达;到了2005年,配装F-22的AN/APG-77多功能机载火控雷达,具有十几种工作模式,雷达天线直径为1 m,随着芯片集成度的提高和硅功率芯片效率的提升,其重量降为200 kg,减轻了2/3。在民用领域,用于智能驾驶汽车进行车外环境感知的车载雷达是典型的应用,2016年德国大陆公司推出的77 GHz雷达传感器尺寸仅为137 mm×91 mm×31 mm,最大探测距离超过250 m。2019年,Bell实验室发布了基于硅基高集成度芯片的94 GHz相控阵雷达,尺寸仅为32 mm2,比硬币还小[8]。2021年,IMEC发布的145 GHz芯片化雷达,其芯片尺寸仅为6.5 mm2,工作带宽达13 GHz,距离分辨率优于30 mm[9]。由此也可以看出,雷达系统一直向小型化、微型化和高集成方向不断发展,芯片化程度越来越高是重要发展趋势之一。2006年,加州理工学院最早提出将雷达模块包括天线均在硅基片上完成,从而实现了片上雷达(RoC)[10]。利用片上系统(SoC)技术将雷达系统集成在一块芯片上或呈现在一个模组里,形成片上雷达系统是实现雷达小型化的重要途径[11-12],也是目前半导体与雷达技术领域前沿热点研究方向之一。

本文在回顾目前片上雷达技术研究工作的基础上,重点梳理片上雷达技术研究发展路径和技术趋势。探索和提出基于先进硅基集成电路工艺,实现片上集成多路雷达收发前端、波形产生及信号处理等雷达功能单元,同时提出结合异质异构及先进封装技术,将整个雷达芯片集成封装在一个模组内,开发片上雷达系统,实现雷达系统小体积、轻重量、低成本和低功耗,有望为未来小型化武器装备提供有效的探测感知手段,也为蓬勃发展的民用雷达提供可行的技术路径。此外,通过集成电路技术将多个雷达收发前端集成在一颗芯片上,形成可扩充片上模块,基于这些模块也有望构建大型复杂阵列雷达系统,满足军事场景中远距离、多功能、高分辨等应用需求。

1 片上雷达系统架构

1.1 脉冲雷达、调频连续波雷达与调相连续波雷达

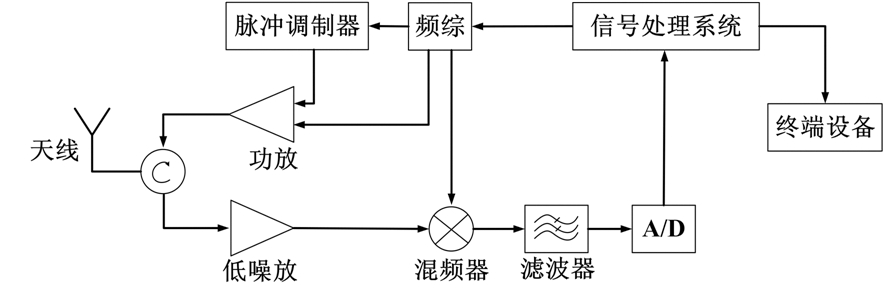

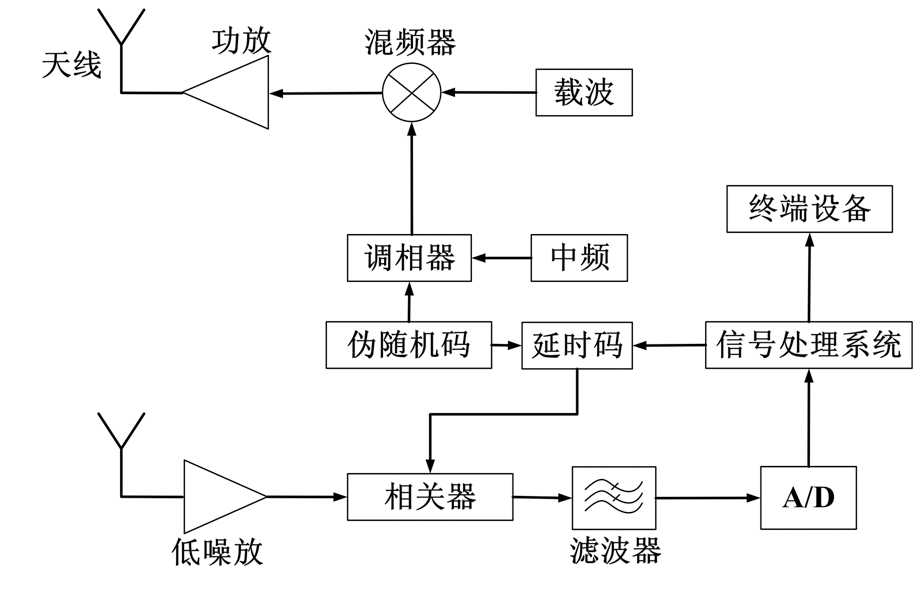

目前常规片上雷达按照信号形式一般可大致分为脉冲雷达、调频连续波(Frequency Modulated Continuous Wave, FMCW)雷达、调相连续波(Phase Modulated Continuous Wave, PMCW)雷达等不同类型,不同类型雷达的基本结构如图1所示。脉冲雷达是目前应用较为广泛的一种雷达,脉冲雷达的发射信号是通过脉冲调制,并经过功放和天线实现脉冲调制信号的辐射,依据多普勒效应检测目标并计算其速度,可满足大多数应用场景。FMCW雷达通过频率差来计算目标距离,但通常目标距离造成的频差和多普勒效应容易混在一起,不易区分开来,FMCW雷达需要发射多个不同斜率的连续波并来解决目标检测模糊和虚假目标问题。在PMCW雷达系统中,发射端的基带产生低频的伪随机码,与本振混频到射频频段,而在接收端将同一个伪随机码与混频后的基带信号进行相关处理,当延时恰好等于电磁波到目标来回的传播时长时,信号处理后输出的信号幅度最大,据此可计算出目标的距离。

(a) 脉冲雷达

(b) FMCW雷达

(c) PMCW雷达

图1 不同类型雷达基本结构

对于片上雷达而言,片上集成功放输出功率有限,达到脉冲雷达的大功率瞬时输出要求较为困难。但是在近距离感知场景,由于输出功率要求大幅降低,脉冲雷达仍然可以实现片上集成,例如,2014年TI Kilby实验室 Ginsburg等人基于65 nm CMOS工艺实现了工作在160 GHz频段的片上脉冲雷达,用于实现短距离应用 [13]。FMCW雷达的基带信号频率低,处理简单,对模数转换器(Analog to Digital Converter, ADC)和数字基带的速度要求小,容易实现小型化集成,在汽车雷达、手势识别等领域广泛应用。2018年TI公司的Ginsburg等人在国际固态电路会议( International Solid-State Circuits Conference, ISSCC)上提出了一种面向汽车雷达的3发4收的FMCW雷达芯片,该芯片基于45 nm CMOS工艺,片上集成多通道FMCW雷达,能够实现高分辨率和适应远、中、近距多模工作 [7]。2016年,谷歌的WANG 等人提出了一种面向手势识别的Soli雷达,该片上雷达采用FMCW架构,能够准确识别按钮、转盘等手势操作 [7]。PMCW雷达相对于FMCW雷达,本振信号源设计更为简单,仅需要一个单频点的本振信号,但接收端的中频频率往往高于FMCW雷达,故需要更高速率的ADC。PMCW雷达易于在MIMO (Multiple Input Multiple Output)雷达阵列中提供所需的正交信号,因此PMCW雷达便于扩展到MIMO阵列中[15]。2017年,IMEC在IEEE固态电路杂志(Journal of Solid-State Circuits, JSSC)上提出一种79 GHz频段片上集成2×2 PMCW雷达SoC架构,单片集成两路雷达发射、两路接收、雷达信号产生、数据采集及雷达信号处理,通过两片雷达SoC级联实现4×4 MIMO系统[16]。

1.2 相控阵雷达

相控阵雷达是发展于20世纪60年代的新型雷达架构,其通过对多个分布式雷达收发通道的相位进行调控实现空域波束形成,能够实现灵活的波束扫描和目标跟踪,为雷达技术的发展赋予了新的生命力。传统的相控阵雷达由于包含了多个分立的收发通道和天线单元,其设备量和体积较为庞大,难以适应无人机、智能汽车、手势识别等体积、成本和功耗受限的应用场景。特别是对于片上雷达系统,受芯片制造工艺和微小体积内热流密度等因素的限制,难以获得高的发射输出功率和低的接收噪声性能。

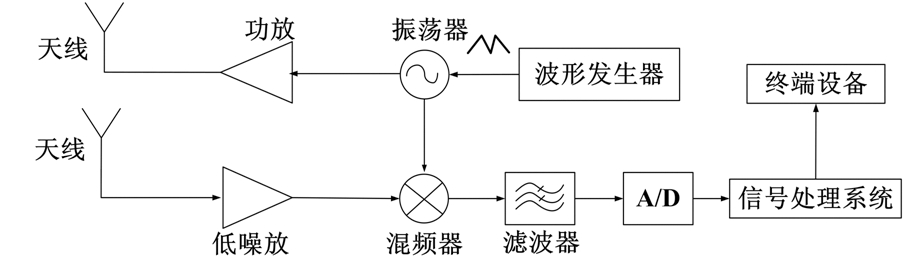

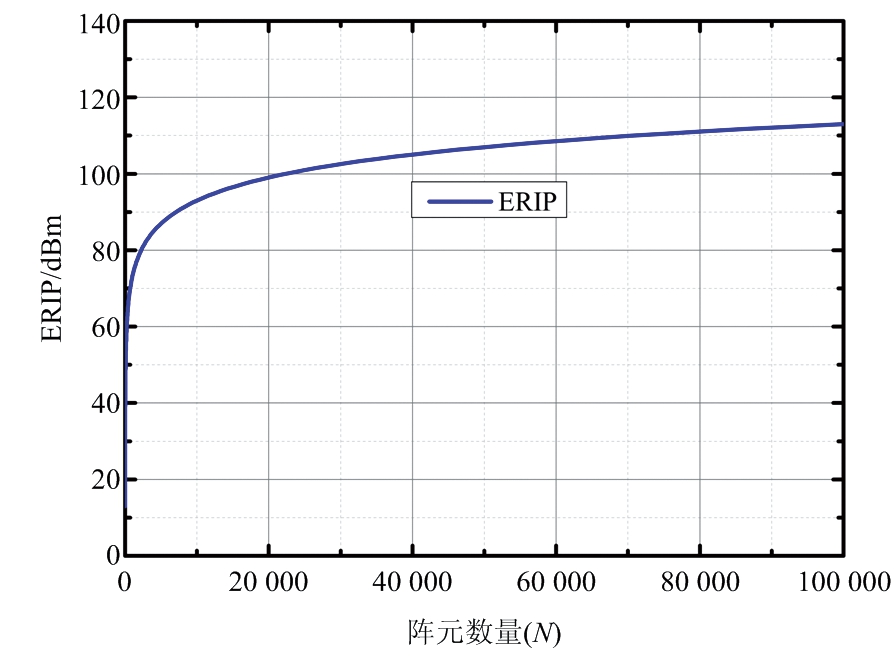

对于一个N个收发单元的相控阵系统,其等效全向辐射功率(Effective Isotropic Radiated Powe, ERIP)可以表示为

ERIP= N2×PTX,single

(1)

式中,PTX,single为单个收发组件的单通道输出功率。

若单个收发组件的单通道接收信噪比(Signal-to-Noise Ratio, SNR)为SNRRX,single,理论上合成以后的信噪比可以表示为

SNROUT=N×SNRRX,single

(2)

根据公式(1)和(2)可以看出,在同样发射功率和接收信噪比的要求下,随着阵元数量的增加,对单通道发射功率和噪声性能的要求可以迅速降低。假设单个发射通道功率为20 mW,从图2可以看出,阵元数量为10万个时,ERIP超过110 dBm,有望实现百公里级的目标探测距离。

图2 阵列雷达发射ERIP与阵元数量的关系

由此可以看出,通过集成电路技术将多个相控阵雷达收发前端集成在一颗芯片上,形成可扩充片上相控阵模块,基于这些模块有望构建大型复杂阵列雷达系统,满足军事场景中远距离、多功能、高分辨等应用需求;其中,大规模毫米波、太赫兹芯片阵列在星载通信和星载雷达中已逐渐推广使用。随着摩尔定理的发展,硅基集成电路射频性能持续提升,同时能实现多单元、多信号单片集成,为实现片上集成相控提供了新的契机。2004年,加州理工大学在ISSC上发布了一块采用SiGe BiCMOS工艺实现的24 GHz相控阵接收机[17]。在此之后美国的UCLA、UC Berkeley、UCSD、GIT,欧洲的IMEC、TU Delft、KU Leuven,日本的TIT,韩国的KAIST,国内的清华大学、电子科技大学等高校和科研院所对片上集成相控阵进行了持续的研究,片上集成阵列规模和性能不断提升[18-22]。直到今天,片上集成相控阵技术仍然是集成电路和雷达领域的重要研究热点。这些研究工作将相控阵架构的片上雷达研究提升到新的水平,促进其在智能驾驶、高精度安检等领域的广泛应用。

2 雷达芯片技术

2.1 片上雷达射频前端

雷达射频前端是雷达系统最重要的功能单元,也是片上雷达集成的关键部分。随着集成电路技术的进步,雷达射频前端开始以GaAs为代表的Ⅲ-Ⅴ族半导体工艺实现,集成度和性能都得到了长足的提升。然而,随着雷达系统向小型化和芯片化的进一步发展,传统化合物半导体工艺难以实现大规模集成,特别是无法实现射频、数模混合及数字电路单片集成。从本世纪初开始,硅基半导体工艺制程进入深亚微米时代,晶体管的工作速度越来越快,越来越多的射频前端芯片采用硅基半导体工艺实现。

2005年,英飞凌等公司开始采用SiGe BiCMOS工艺进行24 GHz和77 GHz毫米波雷达前端设计,并于2008年在国际射频集成电路会议(Radio Frequency Integrated Circuits Symposium, RFIC)上发表了基于SiGe工艺实现的四通道全集成77 GHz雷达前端芯片[23],单片集成了四路雷达收发前端及压控振荡器(Voltage Controlled Oscillator, VCO),如图3所示。

图3 采用SiGe工艺的四通道全集成77 GHz雷达

收发芯片

片上集成相控阵雷达射频前端是目前片上雷达研究的重要领域。早在2004年,加州理工大学就采用SiGe BiCMOS工艺实现相控阵接收机[17]。在此之后,多个研究机构对相控阵雷达射频前端芯片进行了深入研究,典型的工作包括:2009年Kim等人发布基于SiGe工艺的36~38 GHz的4通道相控阵射频前端[24];2010年 Atesal等人提出8通道X/Ku频段硅基相控阵射频前端[25];2012年Kim等人提出基于SiGe工艺的76~84 GHz的16通道相控阵射频接收前端[26];2020年,Kodak等人片上实现64单元双极化相控阵射频前端芯片,并基于该芯片进一步扩充至256单元相控阵阵列[27]。

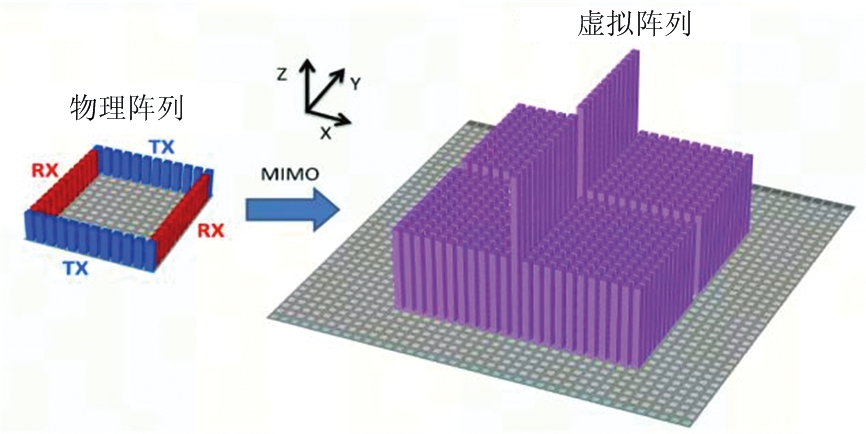

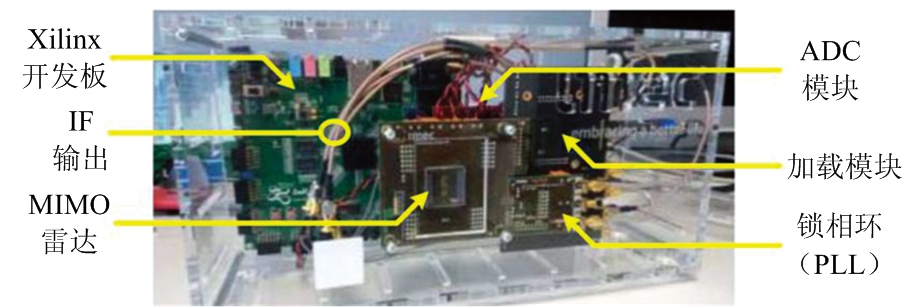

对于片上相控阵雷达而言,每个天线单元对应一路发射/接收通路,为了提高雷达探测能力和角分辨率,需要不断增加天线口径和天线单元数目,这样会造成芯片的复杂度和功耗迅速提升。在相控阵雷达的基础上,采用MIMO技术可以增大天线的虚拟口径,实现高角分辨三维高精度扫描能力。采用MIMO技术还可以大大降低芯片硬件通道的数量,应用潜力极大。文献[28]采用FMCW体制,在16~17 GHz波段,通过24个发射单元和24个接收单元形成576个单元的虚拟阵列并达到了较高的精度。MIMO天线配置及等效虚拟阵如图4所示。

(a) 采用MIMO实现虚拟孔径的原理

(b) 天线阵列

图4 MIMO天线配置及等效虚拟阵

(a) 65 nm CMOS工艺相控阵成像雷达芯片

(b) 28 nm CMOS工艺手势识别雷达芯片模块

图5 采用CMOS工艺雷达前端芯片

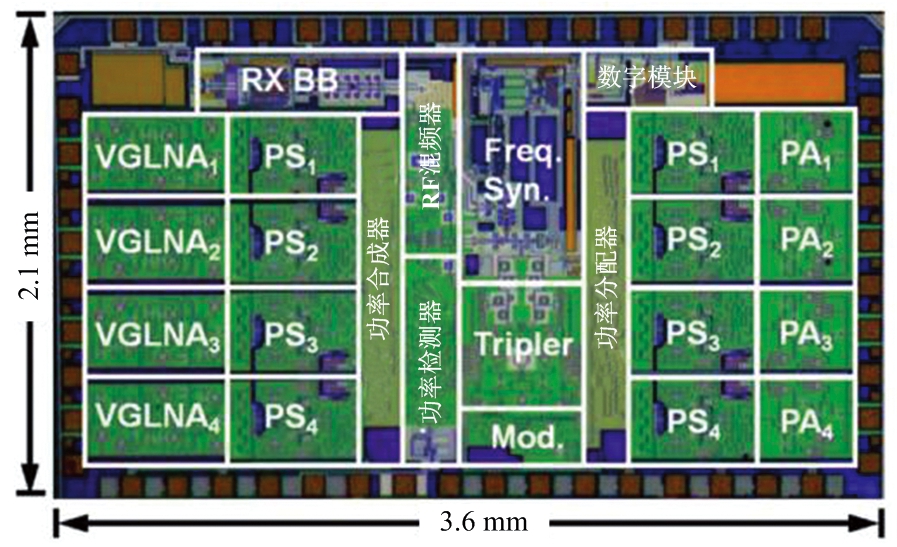

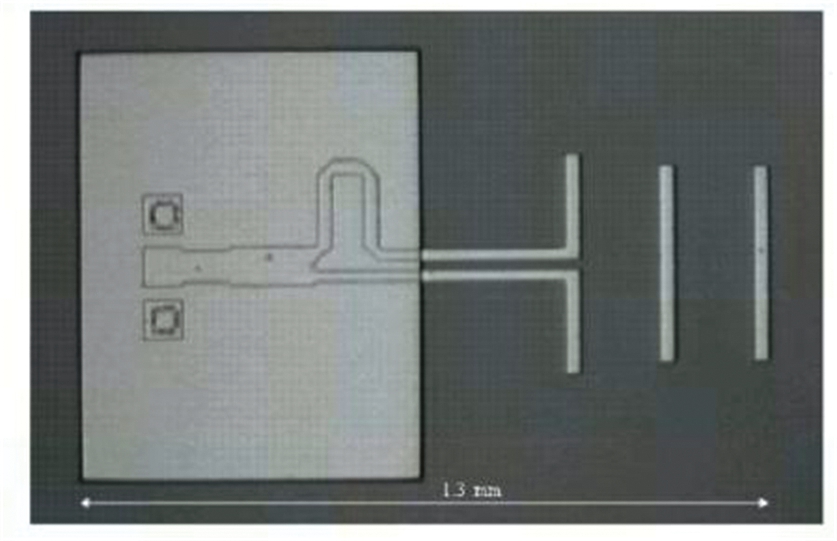

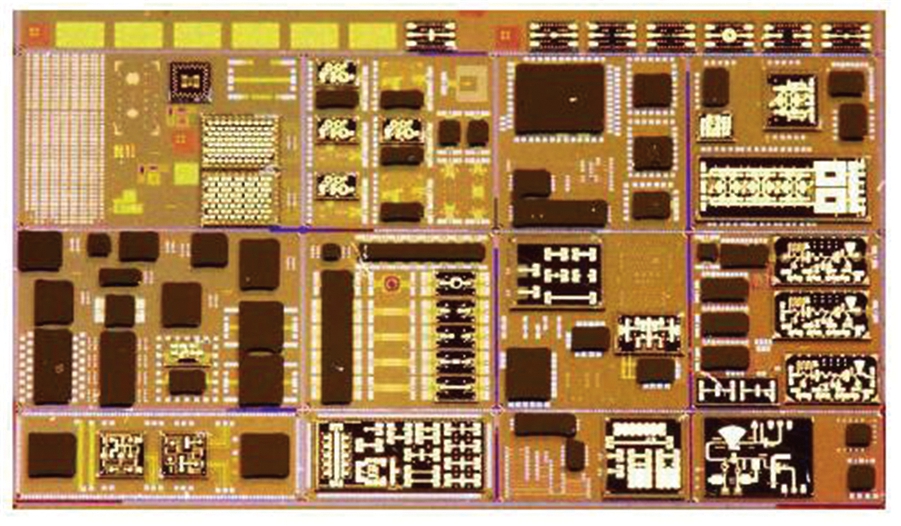

高集成度片上雷达射频前端是应用于高精度成像、手势识别等场景的毫米波雷达核心单元。2015年,台湾大学的Peng 和Lee在JSSC上报道了一款采用65 nm CMOS工艺制造的具有4接收通道4发射通道并能实现3D成像的94 GHz相控阵成像雷达[29],该雷达通过集成的PLL产生高性能脉冲波形测量待测物体。相控阵成像雷达射频前端芯片如图5(a)所示。2021年,IMEC的Viswswaran等人在JSSC上发表了一款用于生命体征检测和手势识别的145 GHz MIMO雷达[9],雷达模块如图5(b)所示,该片上雷达前端基于28 nm CMOS工艺,集成了射频收/发前端。

片上雷达前端在汽车雷达、5G通信、医疗成像、生命体征检测和手势识别等领域得到了广泛的研究与应用,在工作频率上已从毫米波频段覆盖到太赫兹频段,向更高工作频率提升是片上雷达技术的发展趋势,SiGe和CMOS等硅基片上雷达技术是重要发展方向,多通道系统集成的片上雷达前端将是未来的研究重点。

2.2 片上天线技术

随着毫米波芯片技术的发展,毫米波和太赫兹频段雷达在近距离感知和成像等场景展现了较好的应用前景。传统雷达芯片与天线之间通过封装引线及板级过渡互联,在毫米波和太赫兹频段,寄生效应更为明显,装配制造精度要求更为苛刻,成为限制毫米波和太赫兹雷达广泛应用的主要因素之一。由于毫米波和太赫兹频段片上天线尺寸较小,为了进一步提高集成度,同时减小芯片面积以降低成本,人们提出将收发系统以及天线直接集成在一个芯片上,从而提高雷达系统集成度。片上天线(Antenna on Chip, AoC)技术也是目前芯片化雷达领域重点研究问题之一。

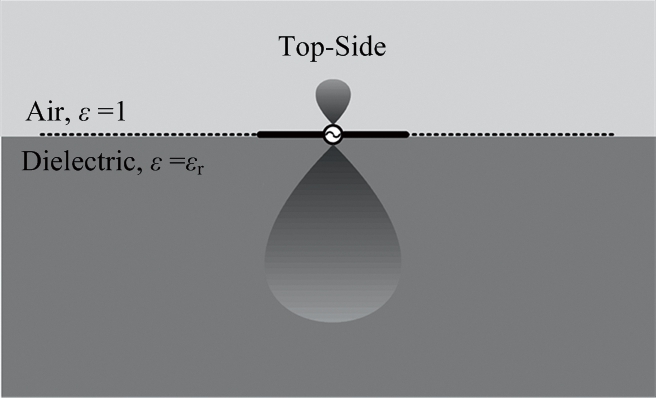

为了提升集成度,片上雷达通常基于硅基半导体工艺实现。然而,硅基材料的低电阻率导致片上天线辐射能量的损失较多,且不能向自由空间辐射,故而面临着辐射增益及效率低等瓶颈问题[30],如图6所示。张跃平等人[31]对衬底减薄、离子注入、微加工和覆盖聚焦等技术进行了总结。提出通过衬底减薄技术降低了衬底对天线的影响,从而提高天线的辐射增益和效率[32],并通过离子注入技术大幅度提高硅基衬底的电阻率,提升了片上天线的增益和效率。

图6 硅基工艺片上天线的辐射情况[29]

(a) 八木片上天线[33]

(b) 添加硅透镜的天线[30]

(c) 加载辐射器的天线[34]

(d) 多馈片上缝隙天线[34]

图7 片上天线设计举例

如图7(a)所示,早期张跃平等人提出60 GHz片上八木天线[33],其效率为5.6%,增益约为-12.5 dBi。如图7(b)所示,为了提高效率,通过在片上天线下方添加高介电常数透镜,可以大幅度改善片上天线的辐射效率和增益,采用这种方法可将天线增益提高10 dB[29]。如图7(c)所示,为了进一步提高天线增益,文献[34]提出在片上加载辐射器方式提高天线增益,加载后的片上天线增益为3 dBi,效率为50%以上。如图7(d)所示,为了在60 GHz频段实现片上天线的功率合成,GiT的Hua Wang团队应用多馈技术的缝隙天线,将多路放大器输出功率馈电到天线上,该方案无需变压器,有效降低系统损耗,提高了系统效率[35]。

2.3 片上信号与数据处理技术

传统雷达主要通过FPGA、DSP等芯片构建的雷达信号/数据处理系统来实现各项处理功能的,这种分立芯片再集成方案,不仅开发复杂,而且成本较高。而片上雷达通过将信号处理模块与雷达射频前端模块进行集成,不仅大幅降低雷达系统体积和功耗,还能简化输入输出接口电路,有效缩短响应时间,提升系统的整体性能。

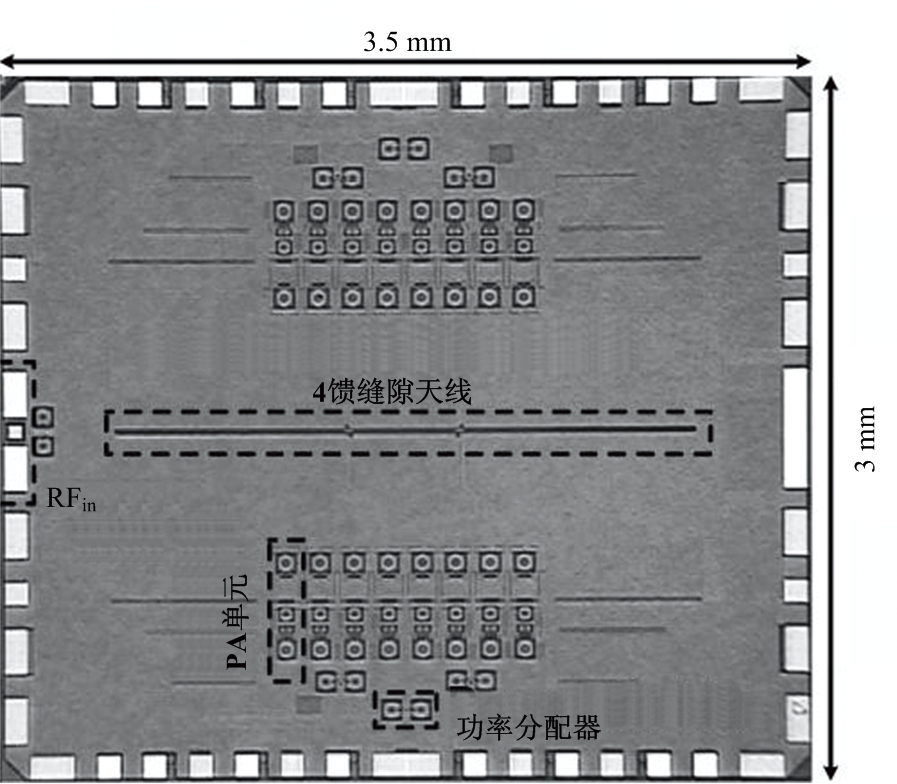

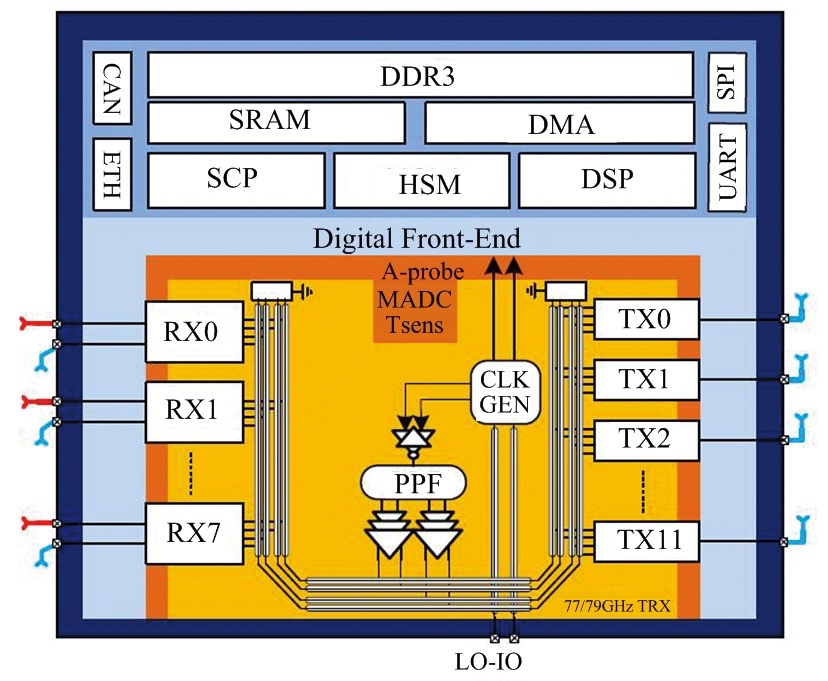

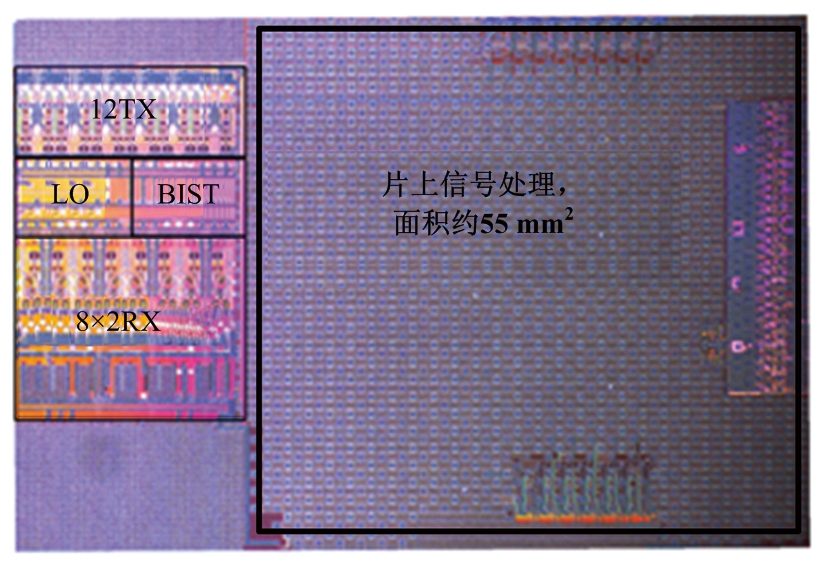

2019年,美国Uhnder公司在ISSCC上发布了一款面向77/79 GHz频段的雷达SoC芯片[36],除了集成收发前端外,片上还集成了PMCW和MIMO雷达信号处理模块,其中包括快速傅里叶变换(Fast Fourier Transformation,FFT)硬件模块、目标检测与分类算法以及外设接口,相对于传统FPGA或者DSP处理方式,实现了信号处理与射频收发前端片上一体化集成,大幅提升了雷达系统的集成度,降低了系统体积、功耗和成本。图8展示的是片上处理和系统整体架构以及芯片照片。

(a) 片上处理和系统整体架构

(b) 芯片照片

图8 美国Uhnder公司发布的77/79 GHz频段的雷达SoC

2021年,谷歌在ISSCC上发布了一款面向手势识别的57~64 GHz FMCW雷达传感器[37],采用FMCW架构,片上集成了1路发射、3路接收、Chirp信号产生及FMCW雷达信号处理模块,并安装于谷歌的手机Pixel 4中,用于识别人的微动手势,从而实现用户对手机的“隔空操作”。

3 异质异构与封装集成技术

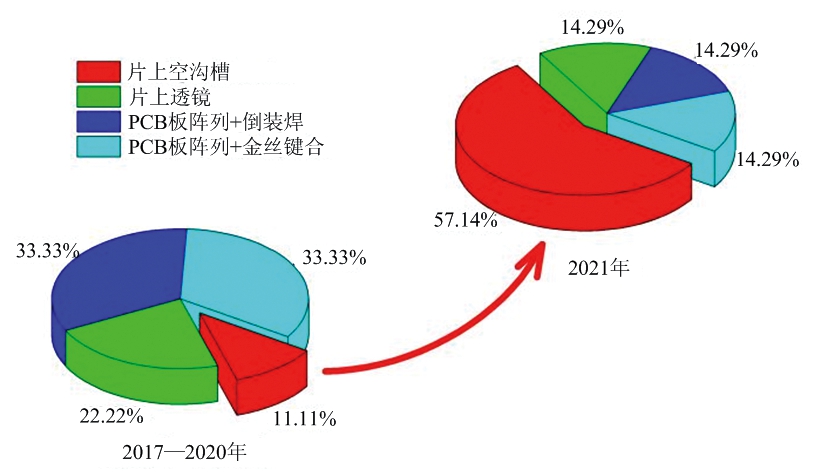

雷达系统包含了天线、射频前端、信号与数据处理等多个不同功能的单元,不同功能和工艺的电路模块有时难以在同一个晶圆上实现集成,特别是功率孔径要求较高的雷达,无法实现单片集成。因此,将雷达系统的各个单元通过异质异构集成实现片上雷达,或者采用封装技术将多个单元集成在一个封装内,是实现雷达小型化的重要技术途径。异质异构集成及先进封装技术可以将不同材质芯片进行三维集成,能够发挥不同材质芯片的优势,同时减小系统尺寸和功耗,提升系统工作的稳定性。图9归纳总结了近5年片上雷达文献中所采用的集成技术[38],早期的片上雷达主要以PCB板级天线加bonding wire封装和PCB板级天线加Flip chip封装为主流,均占比33.33%。随着集成电路技术的发展和雷达工作频段的提升,国内外报道的研究工作更多地采用片上天线方式,实现雷达天线与射频系统的互联,2021年这类研究工作占比达到了57.14%,可以预见未来片上雷达单芯片化是重要的发展趋势。

图9 近5年片上雷达文献里采用的集成技术统计

3.1 异质集成技术

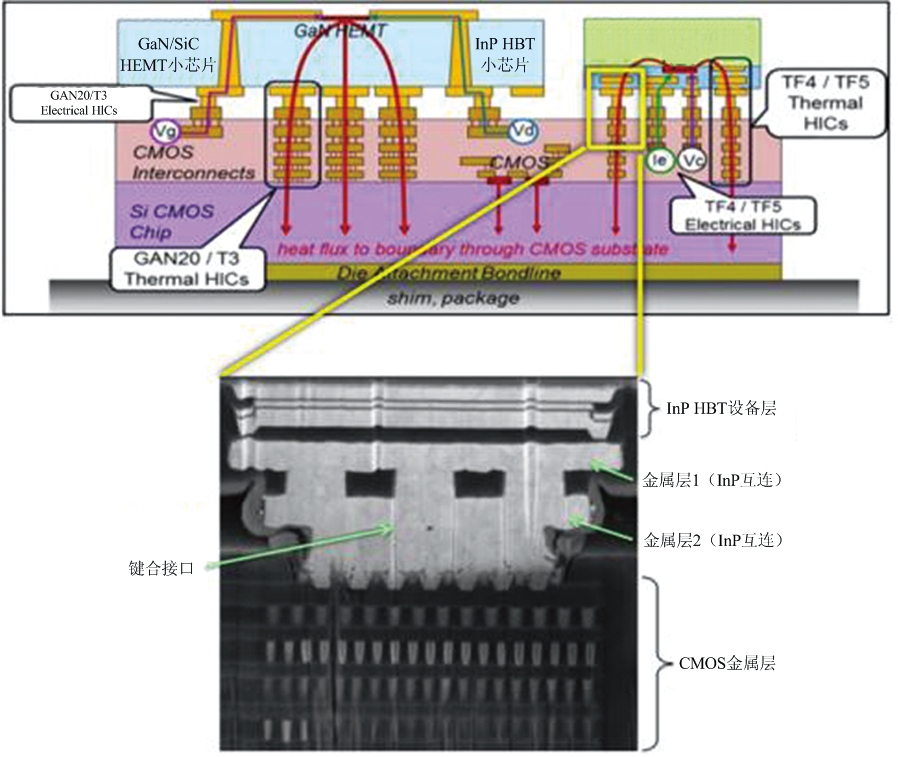

异质集成是将不同材料或者不同工艺的器件集成为一体的技术,晶体管级异质集成技术被DARPA(Defense Advanced Research Projects Agency)认为是实现高性能射频前端的必由之路。如DARPA的“多样化可用异质集成”(Diverse Accessible Heterogeneous Integration, DAHI)项目,体现了DARPA的技术发展策略。DAHI 的硅基化合物半导体材料项目已经证明可以通过多种方式将InP 异质结双极晶体管(HBT)与亚微米硅基CMOS实现异质集成。这样设计者能够将复杂信号处理及自校正架构与高性能化合物半导体电子器件相结合,从而在带宽、动态范围和功耗方面获得大幅的性能提升。通过对新工艺方法的开发,DAHI 项目在65 nm Si CMOS工艺平台上异质集成了0.25 mm的InP HBTs和0.2 mm的GaN高迁移率晶体管,良品率达到99.9%。

2007年,美国学者通过将高速InP HBT器件异质集成到CMOS电路上,实现了一系列先进的自校准和自恢复技术。虽然这些技术不能通过单独的InP基电路实现,但InP基HBT提供了更高的速度、更大的击穿电压和更好的晶体管匹配[39],图10是异质集成截面原理图及扫描电子显微镜图像。

图10 异质集成截面原理及扫描电子显微镜图像

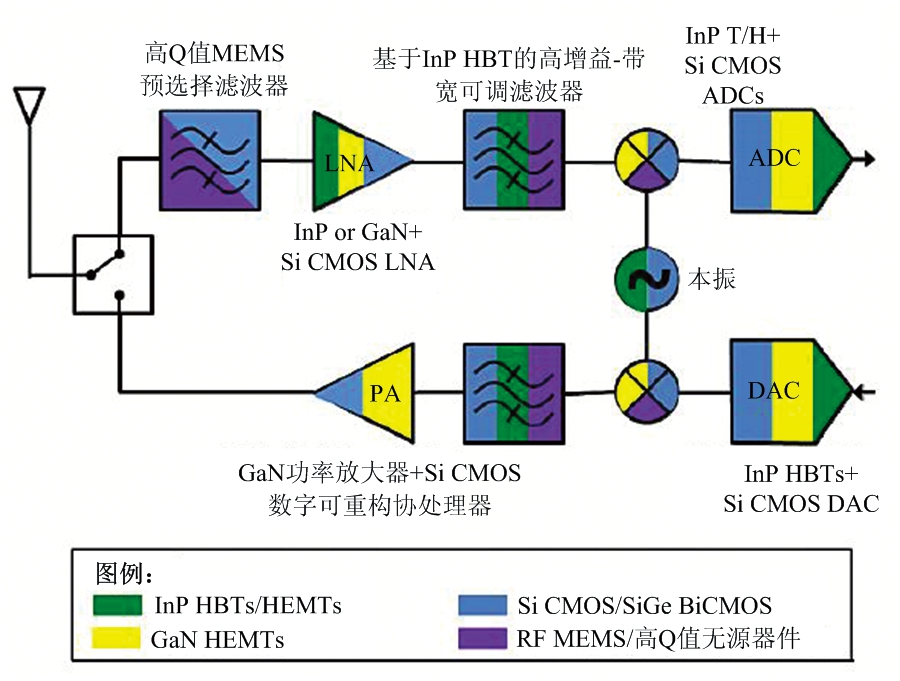

2015年,美国通过DARPA项目开始构建和发展硅基上化合物半导体材料异质集成的FOUNDRY能力,实现了InP、硅基CMOS、GaN和RF MEMS等多项不同工艺灵活多样的异质集成。图11是利用异质集成技术实现的一个典型的收发机系统[40]。

(a) 原理框图

(b) 异质集成收发机系统

图11 异质集成的片上雷达收发机

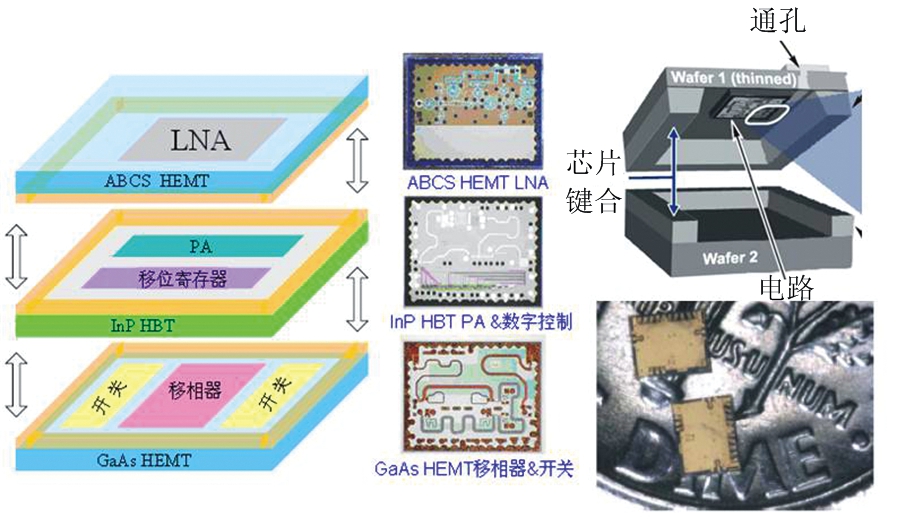

3.2 异构集成

异构集成技术可以将多种不同材质芯片进行三维高密度集成,是微系统的主流技术发展方向,以3D-TSV、3D-WLP、3D IC为工艺平台的微系统集成/制造技术是国际上当前发展的代表。目前美国在三维硅基异构集成技术方面水平最高。例如:DARPA的可重构毫米波阵列(SMART)计划通过系统级三维集成技术在薄型结构上制造完整的T/R组件,提高毫米波天线的集成水平,在0.5~10 mm的厚度上实现了5 W/cm2的功率密度,在与单片集成面积相当的情况下,实现了与传统分立模块搭建的射频前端相当的输出功率。并快速开发出了目前最小封装的多波段芯片阵列,实现可重构多波段相控阵系统。如图12(a)所示,SMART项目在薄型结构上制造完整的T/R组件,实现了芯片化可扩充雷达阵列前端 [41],此外,DARPA在三维电磁射频系统(3D MERFS)计划中,采用MEMS工艺,将毫米波雷达和通信系统的体积、重量和成本的降低幅度达到20倍以上;在传感器结构一体化一体化(ISIS)计划中,诺格公司成功利用WLP和3D堆叠技术实现小型化的X波段芯片化T/R组件,重量小于15 mg,尺寸仅为2.5 mm×2 mm ×0.46 mm,如图12(b)所示。

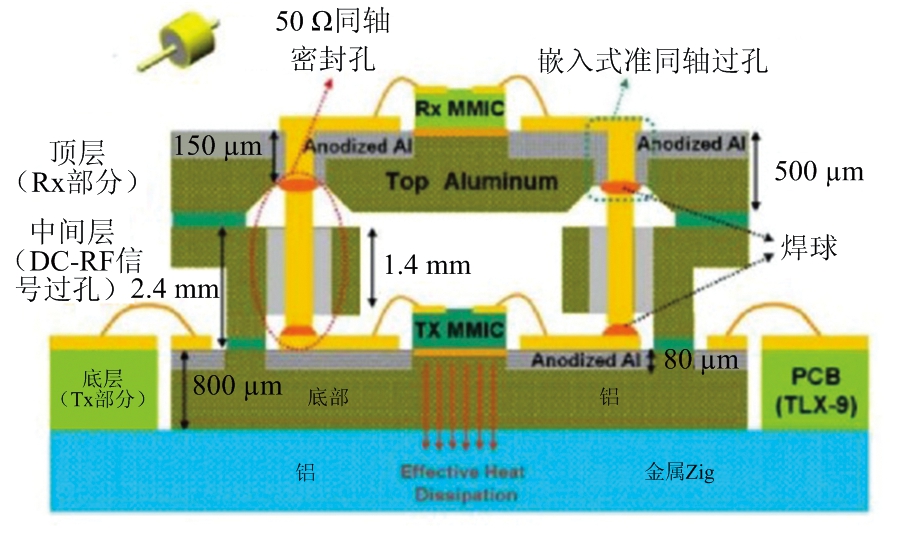

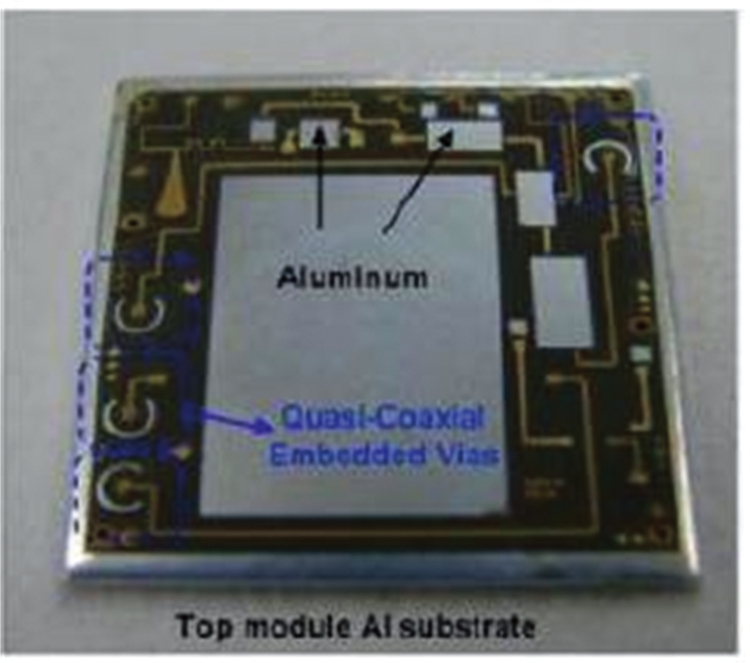

2018年,韩国的Yeo等人采用具有选择性的氧化铝基衬底,实现具有3D架构的芯片级X波段T/R组件,如图13所示[42]。整个一体化封装腔体内包含发射模块、接收模块和其他互连模块,这些模块均采取倒装芯片技术集成到一体化封装内,封装尺寸为20 mm×20 mm×3.7 mm,封装体积比二维结构缩小了67.4%。

(a) SMART计划研制的芯片化可扩充雷达阵列前端

(b) ISIS计划研制的X波段芯片化雷达T/R组件

图12 DARPA支持的面向芯片化雷达的异构集成项目

(a) 三维封装结构

(b) 实物图

图13 选择性氧化铝 T/R组件

3.3 先进封装技术

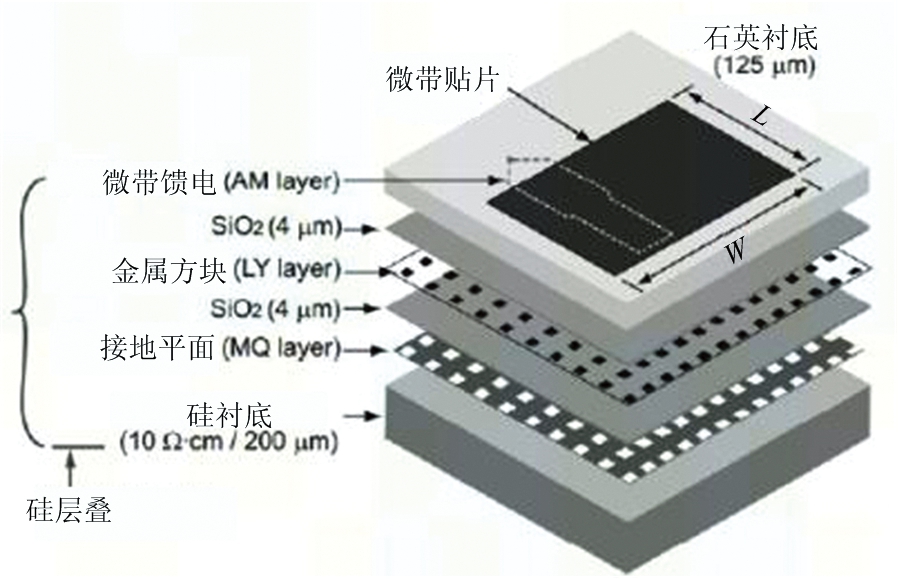

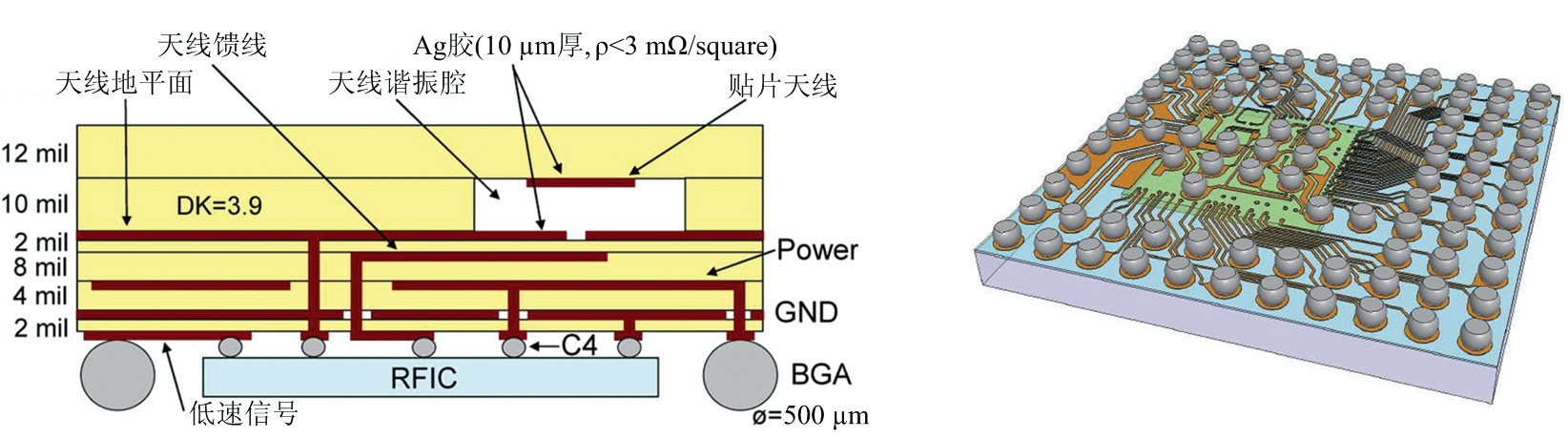

传统的低成本芯片级封装(如QFN、BGA等),一般工作频率较低、管脚密度有限,无法适应雷达系统高频段小型化的发展趋势。采用低温共烧陶瓷(LTCC)技术,可以有效集成雷达前端芯片、无源器件及天线,具有较好的射频性能,是雷达芯片化集成的重要技术手段。图14是用LTCC和晶圆级封装的SiP系统,采用孔径耦合的贴片天线在60 GHz频段上实现5 dBi增益[43]。

图14 采用LTCC和晶圆级封装的SiP系统

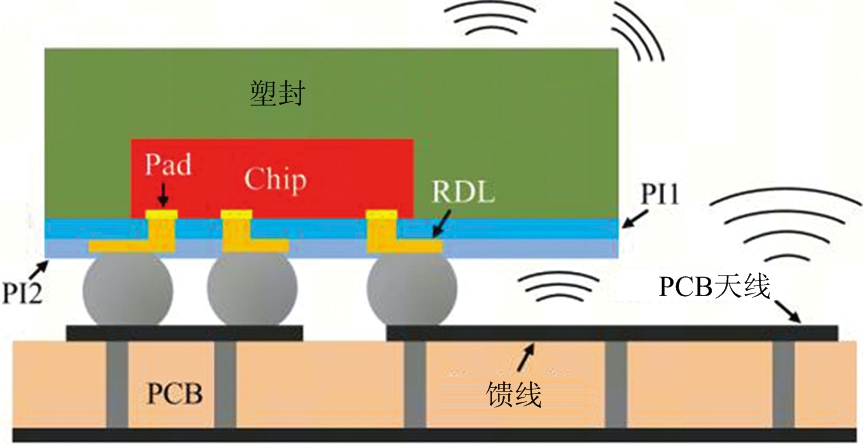

由于采用印刷电路工艺的LTCC技术在线宽、间距和过孔制作方面具有较大的局限性,采用半导体工艺为基础的硅基封装技术得到更大的发展。以TSV技术为代表的2.5D转接板和晶圆级封装(Wafer Level Package,WLP)技术可以有效实现异构器件的三维集成。近期涌现出大量基于扇出封装的雷达模组[3,44-47]成功案例,通过芯片-封装-PCB的一体化设计,有效解决毫米波频段三者之间寄生效应和损耗大等问题,并通过在封装中优化枝节方法解决通道间低隔离度等问题。

在毫米波频段,由于天线单元间距和尺寸较小,在封装内集成天线是片上雷达系统集成的重要发展趋势。如图15(a)所示,芯片PAD上毫米波信号通过扇出型封装的RDL层引出,同时天线也在RDL层实现,从而实现有源芯片、馈线与天线一体化单封装集成。然而,毫米波频段扇出型封装内会产生较多的寄生辐射,运用芯片-封装-天线整体化设计,能够降低芯片封装对天线辐射方向图的影响,再通过优化天线结构可以有效提高天线性能[46]。图15(b)显示了集成2×8单元MIMO阵列封装天线的77 GHz雷达模组[3]。该结构在封装内部实现了多馈天线,代替传统变压器完成了功率合成功能,并在扇出封装内实现MIMO功能,有效提高系统距离和角度分辨率,并极大减小了系统尺寸。

(a) 封装模组剖面图及芯片-封装-天线之间寄生辐射

(b) 集成2×8封装天线的77 GHz雷达芯片

图15 有源芯片、馈线与天线一体化单封装集成

4 片上雷达技术发展趋势

可以看出,无论是军用领域还是民用领域,片上雷达技术都呈现了蓬勃发展的趋势。高集成度射频毫米波芯片技术、数模混合SoC芯片技术的快速发展,异质异构集成、3D封装等先进封装技术的不断进步,是片上雷达技术发展的重要技术驱动力。微型化武器装备、智能感知场景、高精度探测/检测等应用场景仍将持续牵引着片上雷达技术进一步发展,预计未来的片上雷达技术发展主要呈现以下趋势。

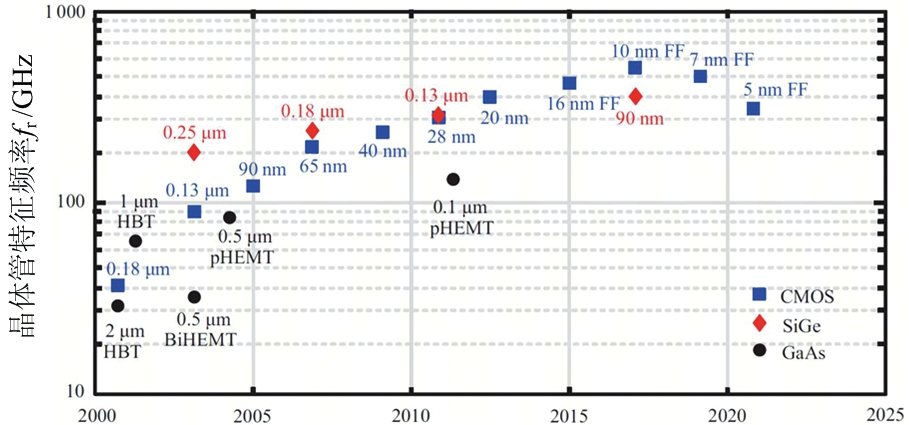

4.1 硅基集成电路工艺成为主流

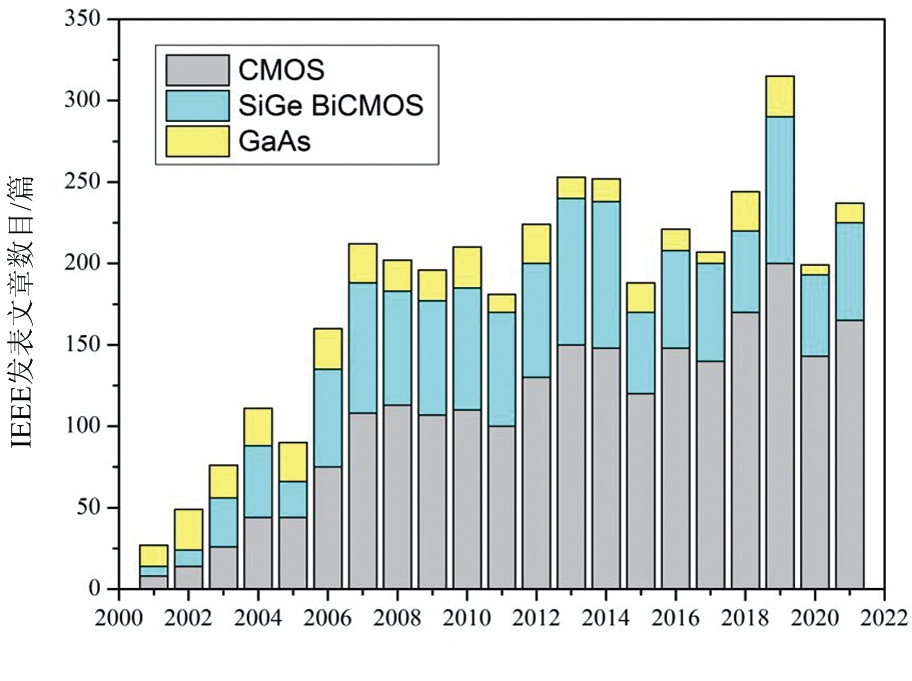

随着晶体管特征尺寸不断缩小,硅基集成电路工艺在集成度、功耗、制造成本等方面都具有明显优势。CMOS集成电路技术在过去的几十年里从平面FET器件发展到了FinFET器件,如今的GAA工艺甚至可以实现1 nm器件。除了CMOS工艺外,SiGe和BiCMOS双极型电路具备优异的高频性能和强电流驱动能力。如图16[48]所示,应用于片上雷达的主流CMOS工艺,其中65 nm、40 nm和28 nm,fT和fmax均超过200 GHz,其噪声性能也比较优异,均能够用来设计较高性能的片上雷达。硅基工艺凭借着其制造成本低,同时能实现与大规模数字电路集成等特点,使得采用硅基技术实现片上雷达的研究成为主流趋势。目前SiGe 130 nm和CMOS 65 nm、45 nm和28 nm已成为片上雷达主要的工艺。虽然基于GaAs工艺的雷达芯片仍有很多,但近年来硅基雷达芯片的数量也呈现快速增长趋势,如图17所示,从2005年,硅基芯片的雷达开始崭露头角,到2022年硅基雷达的数量达到本世纪初的20倍,硅基雷达芯片越来越受到产业界和学术界的青睐[38,49]。

图16 半导体工艺发展

图17 已发表基于硅基和砷化钾芯片的雷达IEEE文献数量

4.2 SiP/SoC是重要发展趋势

雷达系统一直向高集成、小型化方向不断发展,集成化程度越来越高是其重要发展趋势。图18梳理了近10年国内外在ISSCC、JSSC、T-MTT等主要会议和期刊上发表的雷达系统的典型研究工作,早期的研究工作主要是以雷达功能单元和子系统集成为主,随着集成电路技术和先进封装技术的进步,近几年SiP甚至SoC形态的片上雷达已经开始出现,在尺寸、功耗等要求苛刻的平台或者设备上的应用越来越广泛。

图18 雷达集成化发展趋势

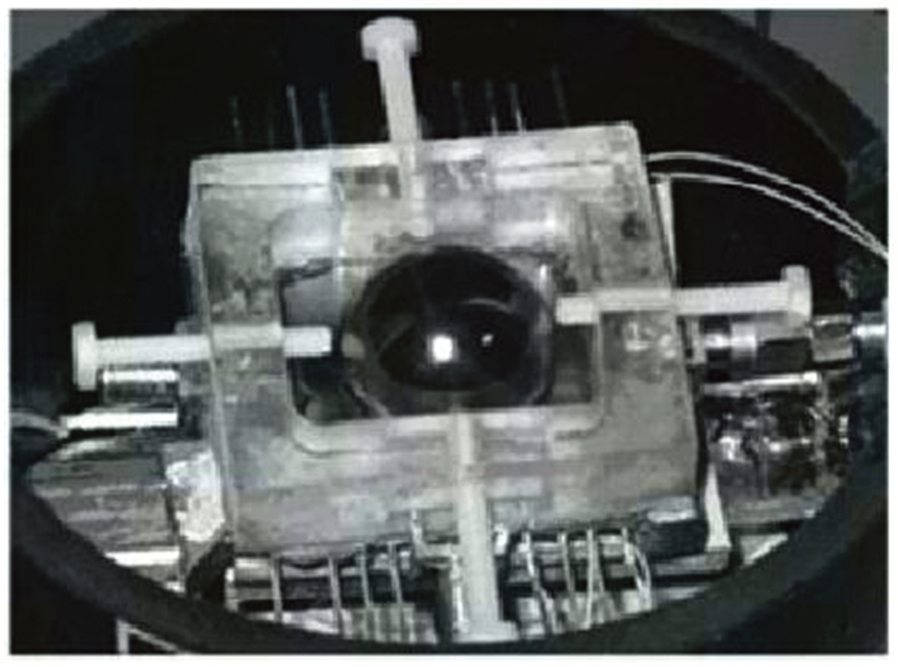

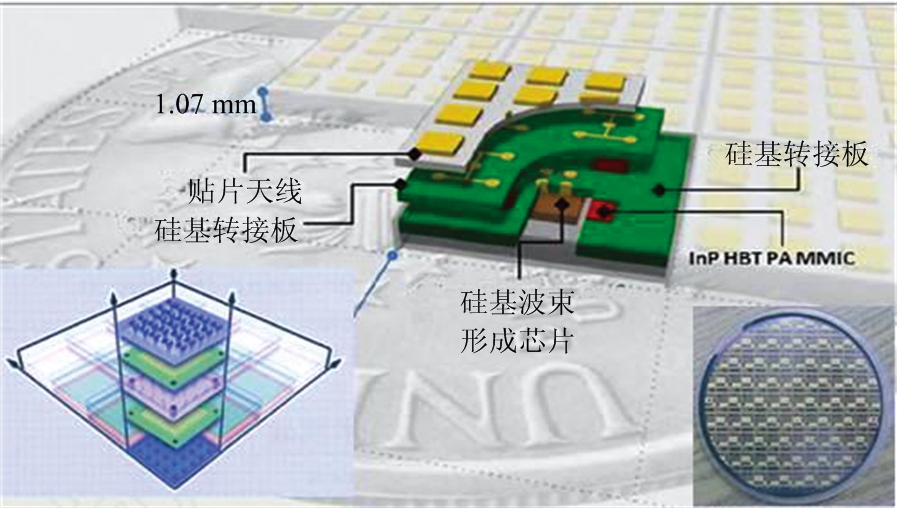

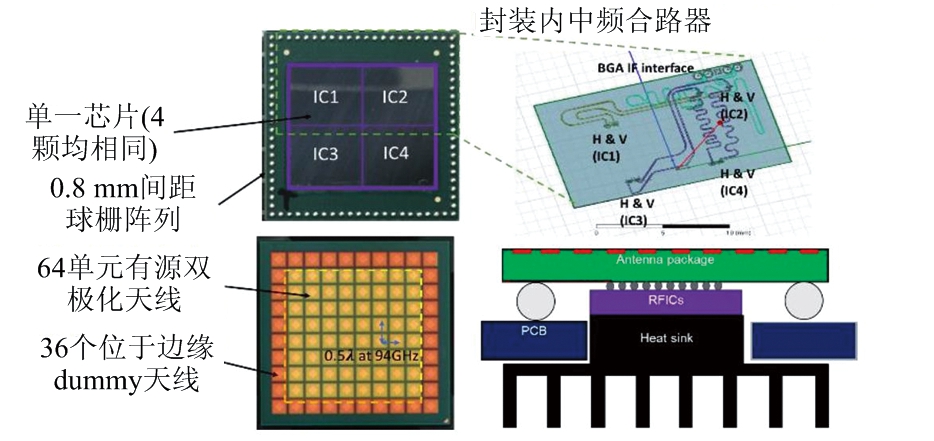

2017年,IBM发布了一款工作于94 GHz频段的SiP雷达,在单个封装内集成了4个32通道相控阵收发前端芯片、32路双极化patch天线单元,实现了厘米级的距离精度和3D成像能力[50],如图19所示。

图19 94 GHz相控阵雷达SiP

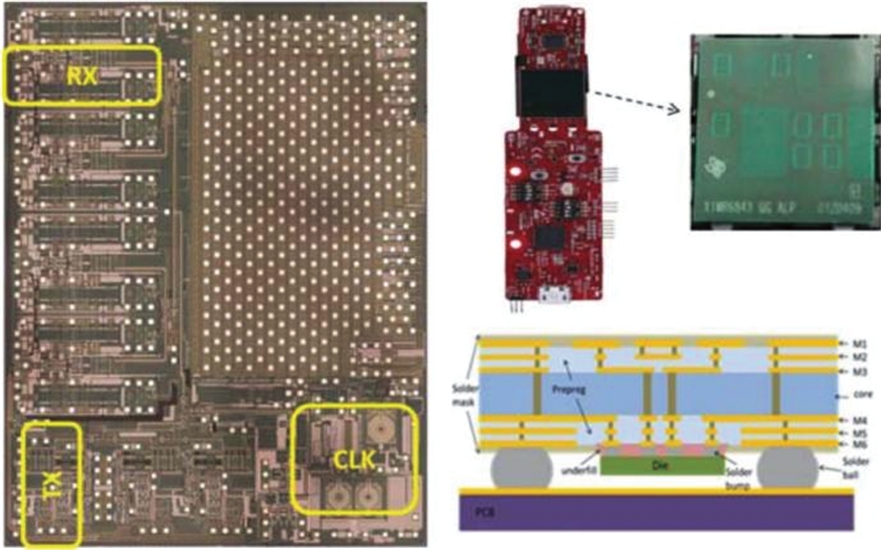

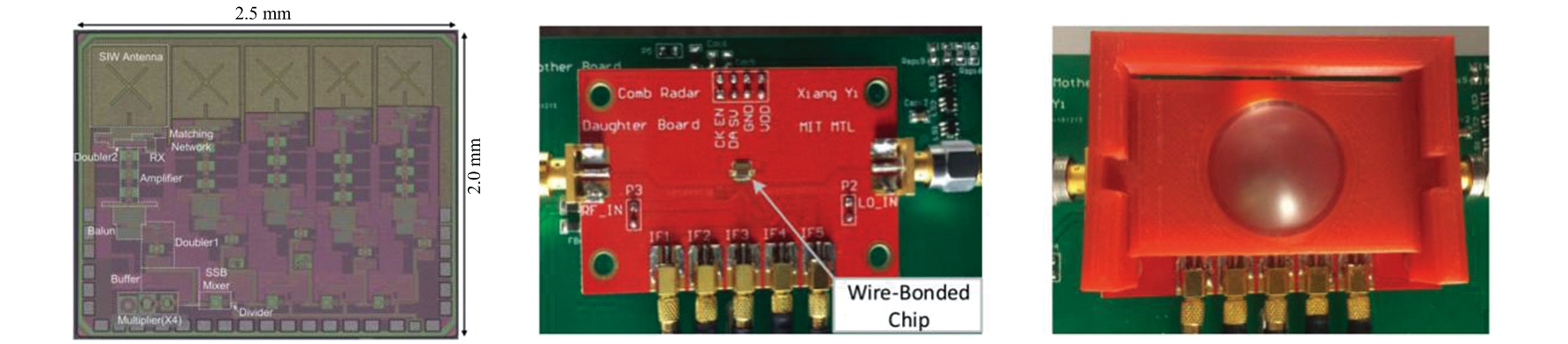

2017年,美国伯克利无线研究中心采用130 nm SiGe BiCMOS工艺设计了一款针对移动设备的手势识别应用芯片,其为94 GHz频段的FMCW雷达的相控阵收发机芯片[51]。该芯片单元输出功率为6.4 dBm,单边带噪声在94 GHz处为12.5 dB,芯片面积为7.4 mm2。集成芯片和天线的雷达模块照片如图20所示。

图20 集成芯片和天线的模块照片

2021年,美国TI公司发布了一款基于45 nm CMOS工艺76~81 GHz的FMCW汽车雷达SoC[52]。雷达的芯片照片及天线封装如图21所示,该雷达通过优化降低了晶体管栅电阻,在不增加功耗的情况下提高了系统性能,在140 ℃温度下可提供大于12 dBm的输出功率。

图21 76~81 GHz雷达SoC芯片照片和含有天线的封装横截面

4.3 工作频段持续提升,异构融合值得关注

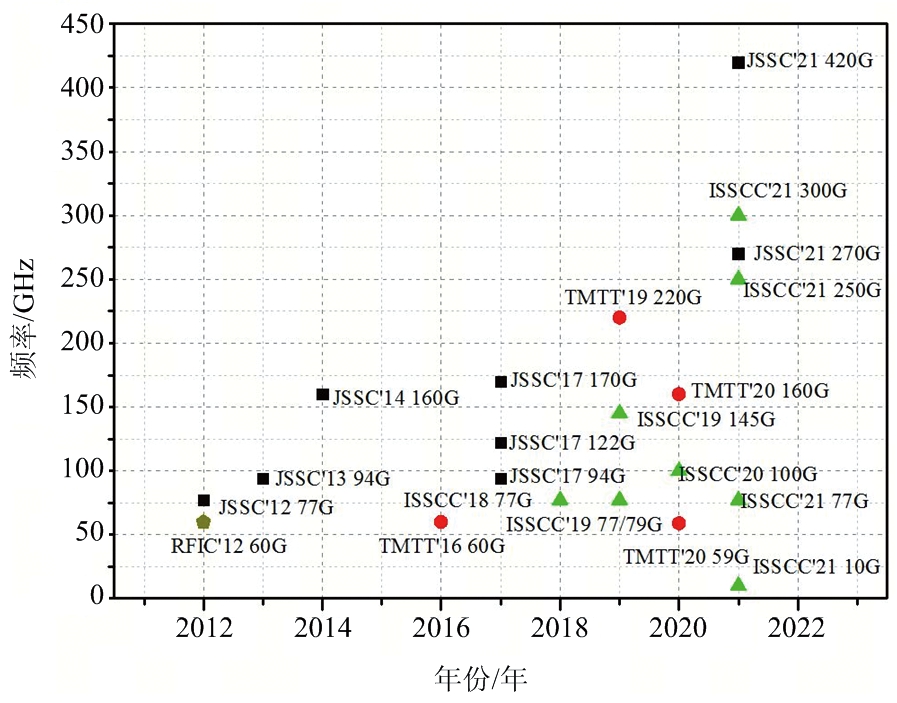

工作频段的提升使雷达可更容易获得大的瞬时带宽,从而探测精度和成像能力得到了提升;同时,高频段芯片有源电路、无源电路及天线的尺寸都大幅减小,更有利于实现小型化和片上集成。因此,更高的工作频段、更强的感知能力是片上雷达的重要发展趋势。图22反映了自2012年以来TMTT、RFIC和JSSCC发布的与片上雷达相关的典型研究工作。可以看出,早期片上雷达的前沿研究主要集中在100 GHz以下工作频段,而近期的研究工作已经突破400 GHz,这一研究动向也符合片上雷达未来发展趋势。

图22 片上雷达发展趋势

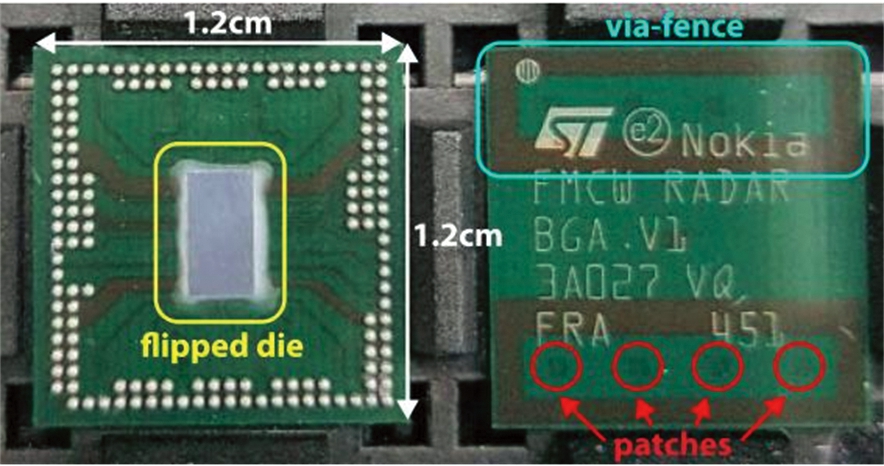

2017年,德国的IHP公司基于130 nm SiGe BiCMOS实现了一款多用途全差分的可扩展雷达系统[53]。该系统可以工作在61 GHz和122 GHz,可适用于对动态范围和分辨率有不同要求的应用场景。2021年,麻省理工学院基于65 nm CMOS工艺实现了一款1.5 mm距离分辨率的220~320 GHz太赫兹FMCW梳状雷达[54],电路框架和版图如图23所示。该雷达采用5个具有等间隔载波频率(梳状)的收/发单元阵列同时扫描,每个收/发单元具有单独的天线。与独立收/发单元雷达架构相比,这种并行的方案可以实现带宽扩展并在整个频带内具有更平坦的频率响应,且对工艺要求不高。

(a) 整体芯片电路版图 (b) PCB上的太赫兹FMCW梳状雷达 (c) 芯片封装照片

图23 太赫兹FMCW梳状雷达

片上雷达走向毫米波和太赫兹频段可以实现更小的体积和更高的精度,但同时也面临着挑战。在不断提高的工作频率条件下,有源器件模型的有效性和无源器件的损耗逐渐制约了硅基工艺太赫兹电路的发展。为了实现较高的角度分辨率,当从单个通道到阵列芯片的扩展时,需要保证多通道的协同工作,因此对源同步的技术提出了更高的要求。同时,片上集成难以实现高效率、大功率雷达信号发射,成为限制片上雷达探测距离的瓶颈问题。

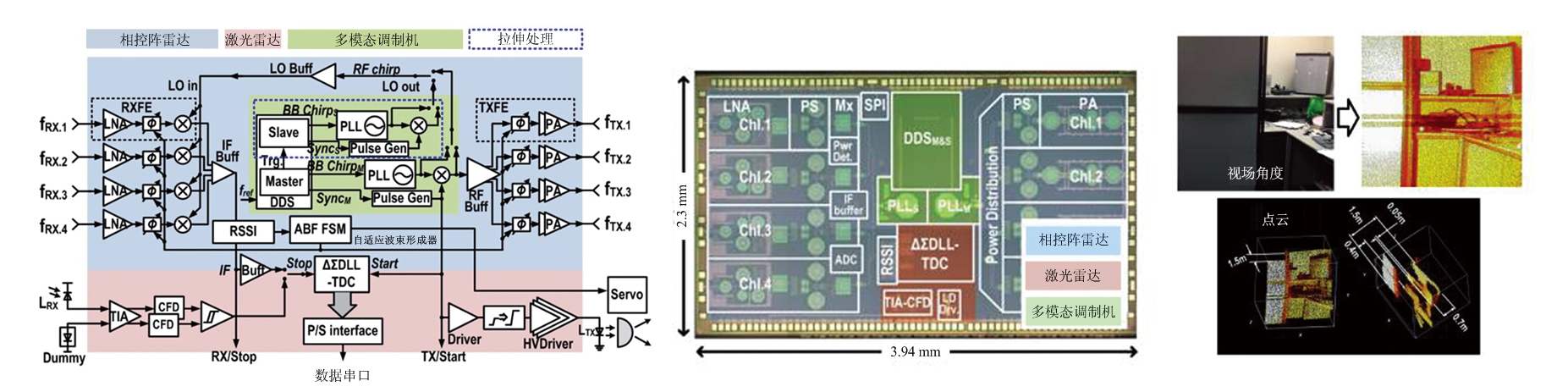

片上雷达另外一个值得关注的发展动态是多传感器融合。通过SoC或者SiP技术,将微波、光学等不同传感器进行融合实现功能互补,能够提升片上雷达传感器的性能并拓宽适用场景。新加坡南洋理工大学在2021年ISSCC上提出了一种融合了微波雷达和激光雷达的片上雷达方案[55],基于65 nm CMOS工艺,将X波段4发4收相控阵雷达前端、雷达波形产生及激光雷达前端实现单芯片集成,在不同应用场景下分别采用调频连续波、脉冲、激光三种模式,距离分辨率最高可达2.1 mm。图24为多模态感知雷达互补传感示意图。

(a) 片上雷达架构 (b) 芯片照片 (c) 成像效果

图24 多模态感知雷达融合

5 结束语

无人机、无人战车和导引头等小型化作战装备在战场中的作用日益凸显,智能驾驶、生命探测和手势识别等产业快速发展,这些场景都对雷达小型化、低功耗、低成本等提出了更加苛刻的要求。微电子和半导体技术进步极大推动了雷达系统向高集成、小型化方向发展,先进集成电路芯片和先进封装技术使得雷达系统集成度越来越高、体积功耗和成本持续降低。本文首先回顾和梳理了当前片上雷达架构和射频前端、天线及信号处理等芯片化研究进展,以及基于异质异构集成、3D先进封装技术的雷达系统集成实现方案。在此基础上,从物理形态、实现工艺及技术发展等方面对片上雷达未来发展趋势进行了分析和展望。

随着晶体管特征尺寸不断缩小,硅基半导体工艺在集成度、功耗、制造成本等方面都具有明显的优势,使得高集成度射频毫米波芯片技术、数模混合SoC芯片技术不断进步,未来基于硅基半导体工艺的雷达芯片将具有广阔的应用前景。同时,异质异构集成与先进封装技术也在不断发展,能够将不同材质芯片进行三维集成,能够发挥不同材质芯片的优势,同时也减小了系统尺寸及功耗。高度集成的硅基雷达芯片,结合异质异构及先进封装技术可以在较小的体积下实现复杂功能雷达芯片,使其在满足复杂多变的电磁环境下的不同应用需求。芯片雷达技术发展有望为未来小型化武器装备提供有效的探测感知手段,也为蓬勃发展的民用雷达提供可行的技术路径。同时,通过集成电路技术将多个雷达收发前端集成在一颗芯片上,形成可扩充片上模块,基于这些模块有望构建大型复杂阵列雷达系统,满足军事场景中远距离、多功能、高分辨等应用需求。

[1] BROOKNER E.Phased-Array Radars: Past, Astounding Breakthroughs and Future Trends [J]. Microwave Journal, 2008,51(1):30-50.

[2] KOH K J, REBEIZ G M. An X- and Ku-Band 8-Element Phased-Array Receiver in 0.18-μm SiGe BiCMOS Technology [J]. IEEE Journal Solid-State Circuits, 2008, 43(6):1360-1371.

[3] DUAN Zongming,WU Bowen,ZHU Chuanming, et al. A 76-to-81GHz 2×8 FMCW MIMO Radar Transceiver with Fast Chirp Generation and Multi-Feed Antenna-in-Package Array [C]∥IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, USA:IEEE,2021:228-229.

[4] HASCH J, TOPAK E, SCHNABEL R, et al.Millimeterwave Technology for Automotive Radar Sensors in The 77 GHz Frequency Band [J]. IEEE Trans on Microwave Theory and Techniques, 2012, 60(3): 845-860.

[5] ARBABIAN A, CALLENDER S, KANG S, et al.A 90 GHz Hybrid Switching Pulsed-Transmitter for Medical Imaging [J]. IEEE Journal of Solid-State Circuits, 2010, 45(12):2667-2681.

[6] PENG Penjui,CHEN Pangning, KAO Chiro,et al. A 94 GHz 3D Image Radar Engine with 4TX/4RX Beamforming Scan Technique in 65 nm CMOS Technology [J]. IEEE Journal of Solid-State Circuits, 2015, 50(3):656-668.

[7] WANG Saiwen, SONG Jie, LIEN J, et al. Interacting with Soli: Exploring Fine-Grained Dynamic Gesture Recognition in The Radio-Frequency Spectrum [C]∥The 29th Annual Symposium on User Interface Software and Technology, Tokyo, Japan:UIST, 2016: 851-860.

[8] SHAHRAMIAN S,HOLYOAK M J,SINGH A,et al. A Fully Integrated 384-Element, 16-Tile, W-Band Phased Array with Self-Alignment and Self-Test [J]. IEEE Journal of Solid-State Circuits, 2019, 54(9):2419-2434.

[9] VISWESWARAN A,VAESEN K,GLASSEE M,et al. A 28-nm-CMOS Based 145-GHz FMCW Radar: System, Circuits, and Characterization [J]. IEEE Journal of Solid-State Circuits,2021,56(7):1975-1993.

[10] NATARAJAN A, KOMIJANI A, GUAN X, et al. A 77-GHz Phased-Array Transceiver with On-Chip Antennas in Silicon: Transmitter and Local LO-Path Phase Shifting [J]. IEEE Journal. Solid-State Circuits, 2006, 41(12):2807-2819.

[11] 贾海昆, 池保勇. 硅基毫米波雷达芯片研究现状与发展[J]. 电子与信息学报, 2020, 42(1):173-190.

[12] 刘兵,李旭光,傅海鹏,等.毫米波雷达前端芯片关键技术探讨[J].电子与信息学报,2021,43(6):1458-1479.

[13] GINSBURG B P, RAMASWAMY S M, RENTALA V, et al. A 160 GHz Pulsed Radar Transceiver in 65 nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2014, 49(4):984-995.

[14] GINSBURG B P, SUBBURAJ K, SAMALA S, et al. A Multimode 76-to-81GHz Automotive Radar Transceiver with Autonomous Monitoring[C]∥ 2018 IEEE International Solid-State Circuits Conference, San Francisco, USA:IEEE, 2018:158-160.

[15] BOURDOUX A, AHMAD U, GUERMANDI D, et al. PMCW Waveform and MIMO Technique for a 79 GHz CMOS Automotive Radar[C]∥ 2016 IEEE Radar Conference,Philadelphia,USA:IEEE,2016:1-5.

[16] GUERMANDI D, SHI Qixian, DEWILDE A, et al. A 79-GHz 2×2 MIMO PMCW Radar SoC in 28-nm CMOS [J]. IEEE Journal of Solid-State Circuits, 2017, 52(10):2613-2626.

[17] GUAN X, HASHEMI H, HAJIMIRI A. A Fully Integrated 24-GHz Eight-Element Phased-Array Receiver in Silicon [J]. IEEE Journal of Solid-State Circuits, 2004, 39(12):2311-2320.

[18] MIN B W, REBEIZ G M. Single-Ended and Differential Ka-Band BiCMOS Phased Array Front-Ends [J]. IEEE Journal of Solid-State Circuits, 2008, 43(10):2239-2250.

[19] KOH K J, MAY J W, REBEIZ G M. A Millimeter-Wave (40-45 GHz) 16-Element Phased-Array Transmitter in 0.18-μm SiGe BiCMOS Technology[J]. IEEE Journal of Solid-State Circuits, 2009, 44(5):1498-1509.

[20] YU Yiming, ZHENG Qingyou, ZHAO Chenxi, et al.A 60-GHz Vector Summing Phase Shifter with Digital Tunable Current-Splitting and Current-Reuse Techniques in 90 nm CMOS [C]∥ 2015 IEEE MTT-S International Microwave Symposium,Phoenix,AZ,USA:IEEE,2015:1-4.

[21] KU B H, INAC O, CHANG M, et al. A High-Linearity 76-85-GHz 16-Element 8-Transmit/8-Receive Phased-Array Chip with High Isolation and Flip-Chip Packaging [J]. IEEE Trans on Microwave Theory and Techniques ,2014, 62(10):2337-2356.

[22] ZHU Wei, LV Wei, LIAO Bingbing, et al. A 21 to 30-GHz Merged Digital-Controlled High Resolution Phase Shifter-Programmable Gain Amplifier with Orthogonal Phase and Gain Control for 5-G Phase Array Application[C]∥2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA:IEEE,2019:67-70.

[23] HANS P F, HERBERT K, HERBERT J, et al. A 77GHz 4-Channel Automotive Radar Transceiver in SiGe[C]∥ IEEE Radio Frequency Integrated Circuits Symposium(RFIC),Atlanta,GA,USA:IEEE,2008:233-236.

[24] KIM J G, KANG D W, MIN B W, et al. A Single-Chip 36-38 GHz 4-Element Transmit/Receive Phased-Array with 5-bit Amplitude and Phase Control [C]∥ 2009 IEEE MTT-S International Microwave Symposium Digest, Boston, MA, USA:IEEE,2009:561-564.

[25] ATESAL Y A, CETINONERI B, KOH K J, et al. X/Ku-Band 8-Element Phased Arrays Based on Single Silicon Chips[J]. 2010 IEEE MTT-S International Microwave Symposium, 2010:1258-1261.

[26] KIM S Y, LNAC O, KIM C Y, et al. A 76-84 GHz 16-Element Phased Array Receiver with a Chip-Level Built-in-Self-Test System [C]∥ 2012 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Montreal, QC, Canada:IEEE,2012:127-130.

[27] KODAK U, RUPAKULA B, ZIHIR S, et al. 60-GHz 64- and 256-Element Dual-Polarized Dual-Beam Wafer-Scale Phased-Array Transceivers with Reticle-to-Reticle Stitching[J]. IEEE Trans on Microwave Theory and Techniques, 2020, 68(7):2745-2767.

[28] GANIS A, NAVARRO E M, SCHOENLINNER B, et al. A Portable 3-D Imaging FMCW MIMO Radar Demonstrator with a 24×24 Antenna Array for Medium-Range Applications [J]. IEEE Trans on Geoscience and Remote Sensing, 2018, 56(1):298-312.

[29] PENG P, CHEN P, KAO C, et al. A 94 GHz 3D Image Radar Engine with 4TX/4RX Beamforming Scan Technique in 65 nm CMOS Technology [J]. IEEE Journal of Solid-State Circuits, 2015, 50(3):656-668.

[30] BABAKHANI A, GUAN X, KOMIJANI A, et al. A 77-GHz Phased-Array Transceiver with On-Chip Antennas in Silicon: Receiver and Antennas [J]. IEEE Journal of Solid-State Circuits, 2006, 41(12):2795-2806.

[31] ZHANG Y P, LIU D X. Antenna-on-Chip and Antenna-in-Package Solutions to Highly Integrated Millimeter Wave Devices for Wireless Communications[J]. IEEE Trans on Antennas and Propagation, 2009, 57(10):2830-2841.

[32] ALEXOPOULOS N G, KATEHI R B, RUTLEDGE D B. Substrate Optimization for Integrated Circuit Antennas [J]. IEEE Trans on Microwave Theory and Techniques, 1983, 31(7):190-192.

[33] ZHANG Y P, SUN M, GUO L H. On-Chip Antennas for 60-GHz Radios in Silicon Technology [J]. IEEE Electron Devices, 2005, 52(7):1664-1668.

[34] MAY J W, ALHALABI R A, REBEIZ G M. A 3 G-bit/s W-Band SiGe ASK Receiver with a High-Efficiency On-Chip Electromagnetically-Coupled Antenna[C]∥2010 IEEE Radio Frequency Integrated Circuits Symposium, Anaheim, CA, USA:IEEE,2010:87-90.

[35] CHI T Y, WANG F, LI S S, et al. 17.3 A 60GHz On-Chip Linear Radiator with Single-Element 27.9dBm Psat and 33.1dBm Peak EIRP Using Multifeed Antenna for Direct On-Antenna Power Combining[C]∥IEEE International Solid-State Circuits Conference, San Francisco, CA, USA:IEEE, 2017:296-298.

[36] GIANNINI V, GOLDENBERG M, ESHRAGHI A, et al. 9.2 A 192-Virtual-Receiver 77/79GHz GMSK Code-Domain MIMO Radar System-on-Chip[C]∥ 2019 IEEE International Solid-State Circuits Conference, San Francisco, USA:IEEE, 2019:164-166.

[37] TROTTA S, WEBER D, JUNGMAIER R W, et al. 2.3 SOLI: A Tiny Device for a New Human Machine Interface [C]∥2021 IEEE International Solid-State Circuit Conference,San Francisco,USA:IEEE,2021:42-44.

[38] AHMAD W A. How Will Radar Be Integrated into Daily Life [J]. IEEE Microwave Magazine, 2022, 69(6):30-43.

[39] GREEN D S,DOHRMAN C L,KANE A S,et al.Materials and Integration Strategies for Modern RF Integrated Circuits[C]∥IEEE Compound Semiconductor Integrated Circuit Symposium, California, USA:IEEE,2014:1-4.

[40] GREEN D S, DOHRMAN C L, DEMMIN J, et al. Path to 3D Heterogeneous Integration [C]∥ IEEE 2015 International 3D System Integration Conference, Sendai, Japan:IEEE,2015:27-29.

[41] ROSKER M J. Technologies for Next Generation T/R Modules[C]∥ IEEE Radar Conference ,Waltham, MA, USA:IEEE, 2007:944-947.

[42] YEO S K, CHUN J H, KWON Y S. A 3-D X-Band T/R Module Package with an Anodized Aluminum Multilayer Substrate for Phased Array Radar Applications [J]. In IEEE Trans on Advanced Packaging, 2010, 33(4):883-891.

[43] KAM D G, LIU D, NATARAJAN A, et al. LTCC Packages with Embedded Phased-Array Antennas for 60 GHz Communications [J]. IEEE Microwave and Wireless Components Letters, 2011, 21(3):142-144.

[44] TONG Z Q, FISCHER A, STELZER A, et al. Radiation Performance Enhancement of E-Band Antenna in Package[J]. IEEE Trans on Components, Packaging and Manufacturing Technology, 2013, 3(11):1953-1959.

[45] ZHANG Y P, MAO J F. An Overview of the Development of Antenna-in-Package Technology for Highly Integrated Wireless Devices[J]. Proceedings of the IEEE, 2019,107(11):2265-2280.

[46] ZHU Chuanming, DUAN Zongming, WANG Yan, et al, Co-Design of High Isolation Chip-Package-Board in eWLB Package for 77 GHz Automotive Radar Application [C]∥IEEE 21th Electronics Packaging Technology Conference (EPTC), Singapore:IEEE, 2019:1-5.

[47] ZHU Chuanming,WAN Yinglu, DUAN Zongming, et al. Co-Design of Chip-Package-Antenna in Fan-out Package for Practical 77 GHz Automotive Radar[C]∥IEEE 71st Electronics Components and Technology Conference (ECTC), San Diego, CA,USA:IEEE, 2021:1169-1174.

[48] 赵涤燹,陈智慧,尤肖虎. CMOS毫米波芯片与4096发射/4096接收超大规模集成相控阵设计实现[J]. 中国科学:信息科学,2021,51(3):505-519.

[49] LIU Bing, MA Kaixue, FU Haipeng, et al. Recent Progress of Silicon-Based Millimeter-Wave SoCs for Short-Range Radar Imaging and Sensing [J]. IEEE Trans on Circuits and Systems-II: Express Briefs, 2022, 69(6):2667-2671.

[50] SADHU B,TOUSI Y,HALLIN J, et al. A 28-GHz 32-Element TRX Phased-Array IC with Concurrent Dual-Polarized Operation and Orthogonal Phase and Gain Control for 5G Communications [J]. IEEE Journal of Solid-State Circuits, 2017,52(12):3373-3391.

[51] TOWNLEY A, SWIRHUN P, TITZ D, et al. A 94-GHz 4TX-4RX Phased-Array FMCW Radar Transceiver with Antenna-in-Package [J]. IEEE Journal of Solid-State Circuits, 2017, 52(5):1245-1259.

[52] DANDU K, SAMALA S, BHATIA K, et al. High-Performance and Small Form-Factor mm-Wave CMOS Radars for Automotive and Industrial Sensing in 76-to-81GHz and 57-to-64GHz Bands[C]∥IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, USA:IEEE,2021:39-41.

[53] NG H J, KUCHARSKI M,AHMAD W, et al. Multi-Purpose Fully Differential 61 and 122 GHz Radar Transceivers for Scalable MIMO Sensor Platforms[J]. IEEE Journal of Solid-State Circuits, 2017, 52(9):2242-2255.

[54] YI X, WANG C, CHEN X B, et al. A 220-to-320 GHz FMCW Radar in 65-nm CMOS Using a Frequency-Comb Architecture[J]. IEEE Journal of Solid-State Circuits, 2021,56(2):327-339.

[55] LOU L H, TANG K, FANG Z Y, et al. An Early Fusion Complementary RADAR-LiDAR TRX in 65nm CMOS Supporting Gear-Shifting Sub-cm Resolution for Smart Sensing Circuits Imaging[C]∥ IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, USA:IEEE,2021:220-222.