0 引 言

现代化战争对作战平台的综合性作战性能的要求在逐步上升,随着武器装备信息化的发展,现代化武器必须适应多功能、一体化的发展趋势。长期以来,机载、舰载、弹载等武器平台的射频传感器都是单独分散在系统中,其功能单一,兼容性差,不能形成高效的统一作战平台[1]。系统中大量的电子设备引发的一个重要问题是天线越来越多,直接导致作战平台重量增加,成本加剧,维护困难。“高集成度”和“综合射频”被认为是解决上述问题的关键手段。

伴随着半导体工艺的发展,芯片制造从早期单一功能集成电路逐步向系统级多功能高集成电路、片上系统(System on Chip)以及系统级封装(System in Package)迈进[2]。其中片上系统多采用CMOS工艺,将射频收发链路和频率合成器集成在单个芯片内,可大大减少对PCB面积和芯片数量的需求,被认为是一种最有前途的高密度集成方式。对于相控阵前端,其频段较高,功率较大,集成难度高,因此单一芯片集成全部功能较困难,采用先进封装及瓦片集成技术能够解决相控阵前端小体积、高功率密度、多功能集成等技术指标问题,并且能够提高系统可靠性及可重构性。先进封装及瓦片集成技术正成为相控阵雷达研发中的重要技术形式。

在此背景下,针对军用电子系统采用数字化技术,强调射频孔径的通用性,根据不同的任务需求采取不同的后端数字处理模式,是军用电子系统发展的必然趋势[3]。从优化空时资源及提高可靠性的角度来讲,采用相控阵体制会具有非常明显的优势,如采用收发全数字波束形成的新一代相控阵,比起传统的模拟相控阵,具有动态范围大、指向精度高、易于支持宽带信号、易于实现同时多波束等优点[4],是军用电子系统发展的重要方向。

目前,数字T/R组件已成为国内外各相关单位的研究热点[5]。李归等提出了一种基于正交投影算法的发射多波束形成和数字时延补偿方法,对发射多波束形成的相控阵方向图性能、波束间隔离、阵列增益损耗以及副瓣性能进行了仿真[6]。Guo等提出了一种用于真空电子器件的2×2输出相控阵雷达的新型功率放大器单元,工作在Ka波段的大功率行波管慢波电路采用双并联微带曲折线[7]。刘明鑫等研究了一种基于射频直接采样的宽带数字波束形成方法,可以实现准确的波束指向和近似理想的主瓣,同时计算量小、工程可实现性较高[8]。

本文研究了一种基于高集成度射频前端(也称“一体化射频前端”)的新型16通道数字相控阵系统,工作在C波段,集成了天线阵面、校准网络、收发信道、波束形成器等部件。该数字相控阵系统的各部件通过瓦片集成方式垂直互联,相比传统的砖块式方案,具有低剖面、通用性强、宽带特性好、易于扩展等诸多优点。

随着微波毫米波器件的日趋成熟,制造成本显著下降,各整机单位对相控阵的开发越来越重视,纷纷要求把传统体制系统陆续改为相控阵体制,相控阵系统将更加广泛地应用于各型导弹、雷达及各种重点工程。本项目研制的数字相控阵适用于以上应用,场景丰富、迭代升级能力强,具有巨大的市场潜力。

1 数字相控阵系统设计

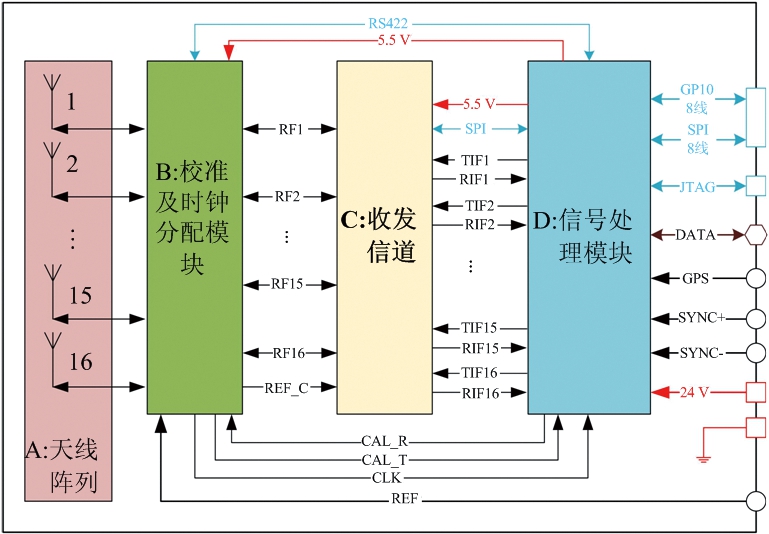

本文设计的数字相控阵系统,可分为射频系统和数字系统两大部分,其核心原理框图如图1所示。

图1 数字相控阵系统原理框图

射频系统主要由天线阵列和收发信道构成,其中天线阵面为4×4面阵,阵元形式为微带天线;校准及时钟模块包括板级校准网络、内外时钟切换和相参时钟产生;收发信道以一体化射频前端为核心,完成信号的上下变频及滤波放大。信号处理模块主要由中频数字信道、数字波束形成模块构成,其中中频数字信道完成抗混叠滤波、AD采样、数字滤波以及发射端波形产生;数字波束形成模块完成收发数字波束形成。

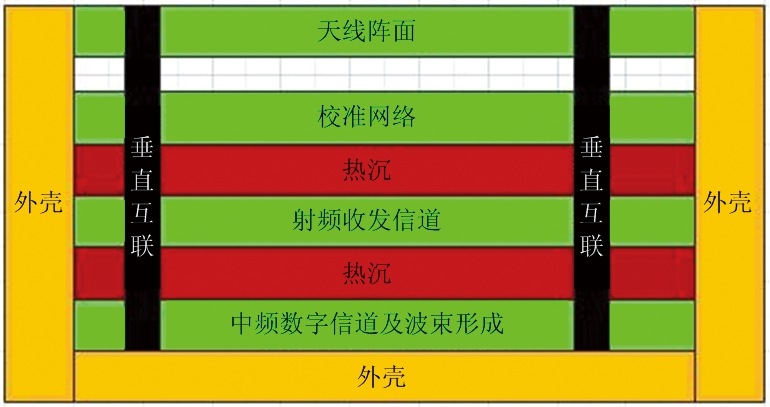

高集成度射频前端集成了功放、可调衰减器、低噪放、混频器、锁相环等大部分射频通道器件,大大简化了外围器件数量和设计难度。因此射频收发通道可以设计得非常紧凑,只占用很少的PCB面积,基于此,本文设计的数字相控阵系统方式采用瓦片式垂直互联进行整体集成,集成方式如图2所示。

图2 数字相控阵的集成方式

2 阵列天线设计

根据数字相控阵系统的指标要求,需研制一款窄频带、低副瓣、两维电扫的微带阵列天线。

首先需要确定天线阵列排布及天线单元间距。天线单元间距的选择需满足栅瓣抑制条件,基于方位及俯仰-30°~30°的电扫需求,该天线行、列单元间距均选取为42 mm。至此,天线阵列排布为4行4列,正方形栅格排布,电气口径为168 mm*168 mm。另外,为满足-25 dB低副瓣要求,天线阵列幅度分布采用-26 dB泰勒加权进行设计。

其次需要确定天线单元形式的选择。微带天线包括有很多种,包括微带偶极子天线、微带圆形贴片天线、微带矩形贴片天线等,另外通过加载技术还可以有更多的变形种类[9]。对于贴片天线而言,按其馈电方式又可分为微带传输线边馈、同轴探针背馈和耦合馈电。考虑到该天线的工作频带并不宽,且结构接口便于与后端模块进行对插,天线单元选择常规的微带矩形贴片天线,通过同轴探针从背后进行馈电。这种天线形式体积小、重量轻、易于加工且方便集成。

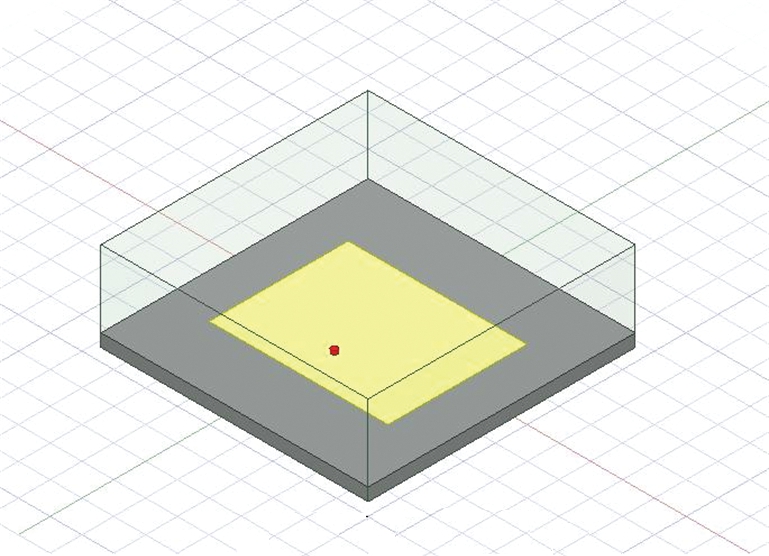

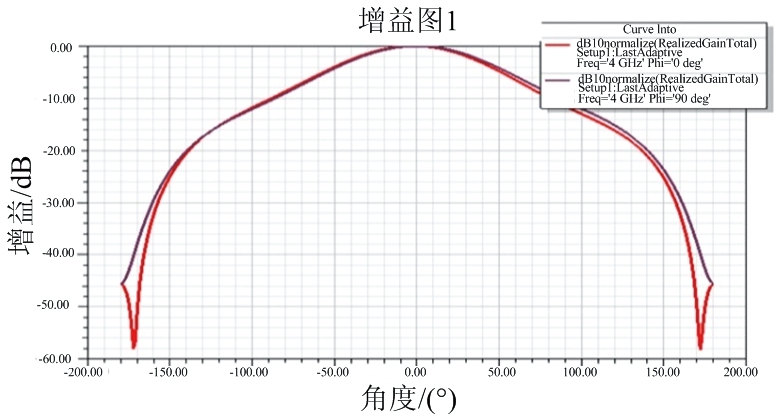

利用电磁仿真软件HFSS对天线单元进行建模仿真。天线单元仿真模型如图3所示,天线单元远场方向图如图4所示。

图3 天线单元仿真模型

图4 天线单元远场方向图

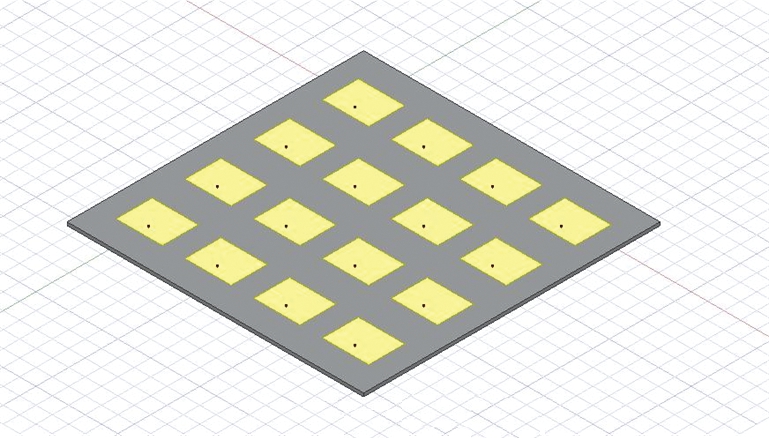

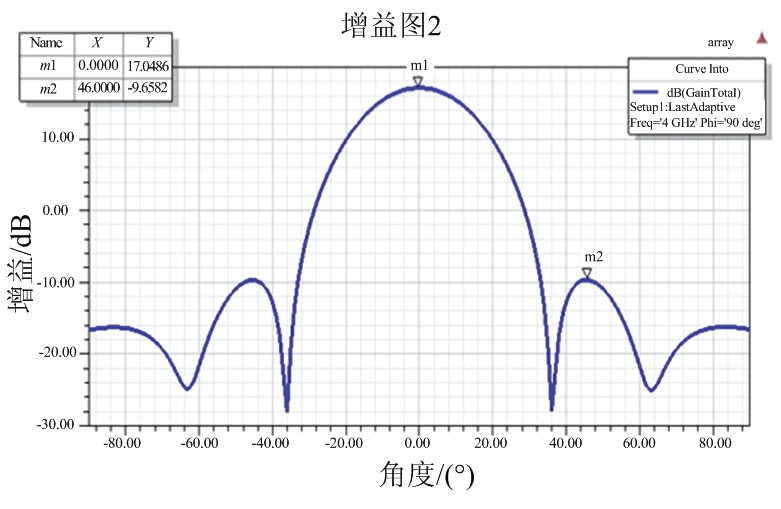

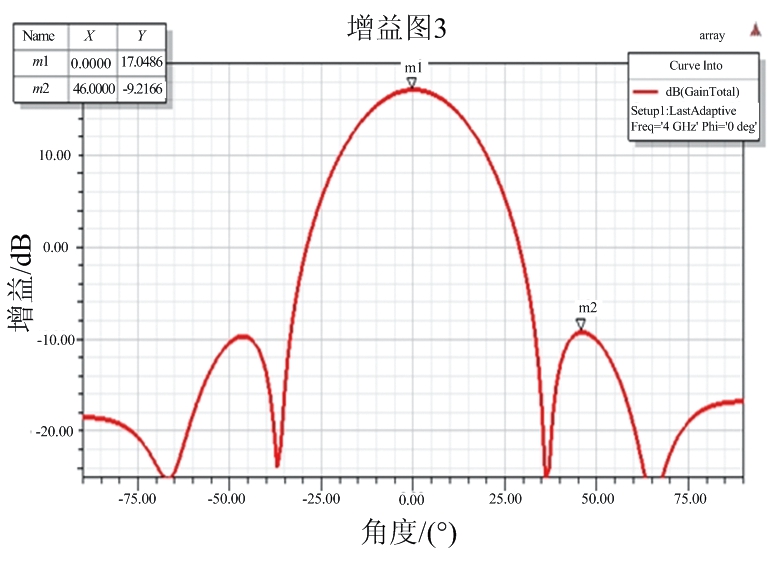

利用仿真软件对天线阵列进行了建模仿真。阵列天线仿真模型如图5所示;图6和图7为阵列天线法向波束方位面及俯仰面的远场方向图。

图5 阵列天线仿真模型

图6 阵列天线法向波束方位面方向图

图7 阵列天线法向波束俯仰面方向图

由扫描波束方向图仿真结果可见,天线增益/副瓣电平/波束指向精度等天线主要指标可满足系统要求。

3 射频通道设计

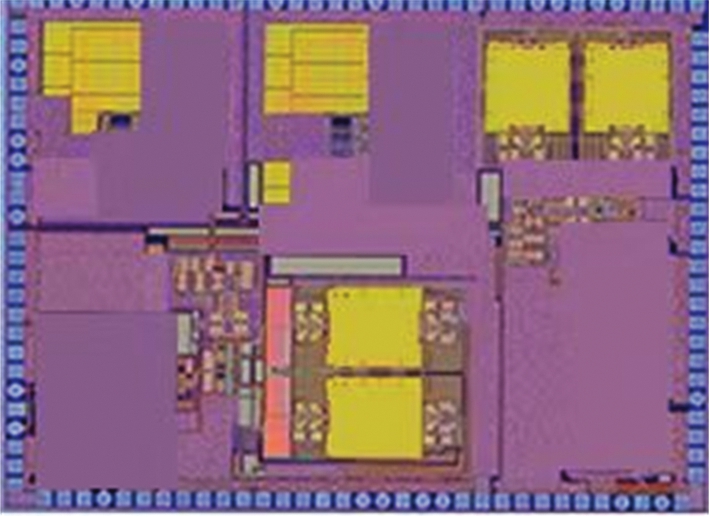

射频通道工作在C波段,工作带宽为80 MHz,核心是高集成度射频前端,其收发通道电路拓扑如图8(a)所示,芯片照片如图8(b)所示。

(a) 高集成度射频前端收发通道电路拓扑图

(b) 高集成度射频前端照片

图8 高集成度射频前端收发通道电路拓扑图及照片

其中接收链路完成C波段信号接收、调理,并下变频到150 MHz中心频率;发射链路完成150 MHz基带信号的上变频、驱动和发射滤波。高集成度射频前端包括TX和RX通道,在TX通道集成了驱动放大器、混频器、发射锁相环、滤波器等器件,在RX通道集成了低噪声放大器、混频器、接收锁相环和滤波器。

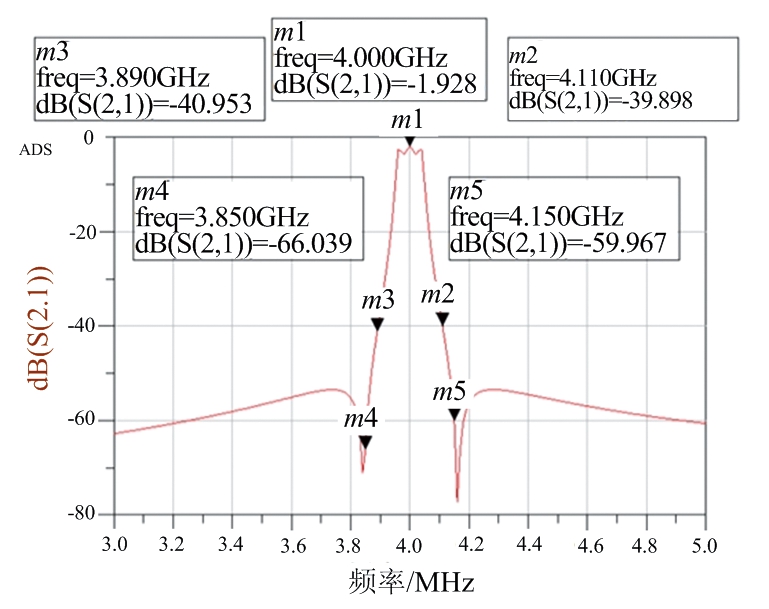

射频收发通道的外围关键器件是射频预选滤波器和中频抗混叠滤波器。其中射频预选滤波器主要保证收发通道的带外频谱特性,即带外杂散的有效抑制度;由于距离边带最近的是三阶交调杂散信号,偏离中心频率为110 MHz,混频器自身可抑制30 dBc,所以预选滤波器在该处抑制30 dBc即可;且本振泄露电平较大,需对本振信号的抑制达到50 dBc以上。则滤波器选择性的设计要求如公式(1),采用介质滤波器实现,其典型频率响应曲线如图9所示。

BW-1 dB≥±40 MHzBW-30 dB≤±110 MHzBW-50 dB≤±150 MHz

(1)

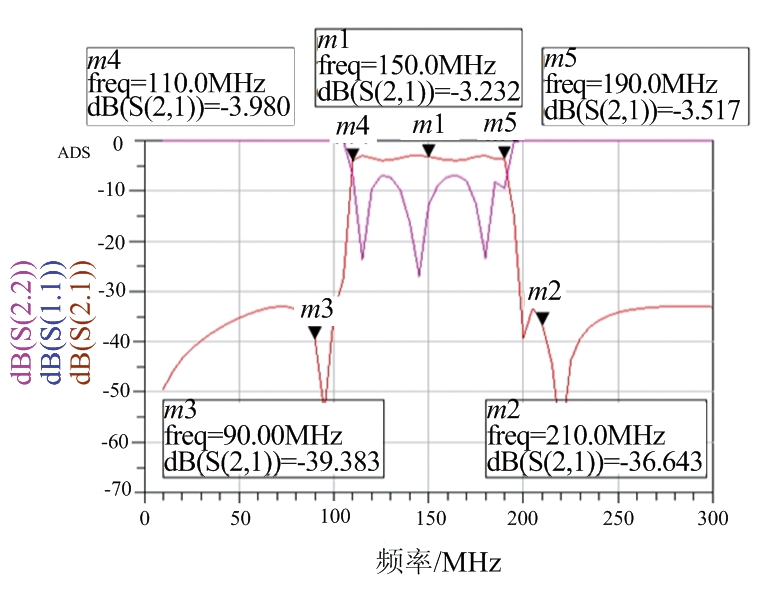

中频处的混频杂散主要集中在频率高端,因此中频滤波器主要限制混频后落入210~290 MHz带内的杂散,需抑制到70 dB以下,以免其混叠后影响有用信号使其失真。落入210~290 MHz带内的杂散主要是四阶交调信号220~380 MHz,混频器自身的四阶交调抑制可以达到50 dBc以上,中频滤波器抑制度达到20 dBc即可,即滤波器的BW-20 dB=±70 MHz。采用LC方式即可实现中频滤波器,其典型频率响应如图10所示。

图9 射频预选滤波器频率响应

图10 中频滤波器频率响应

4 数字中频设计

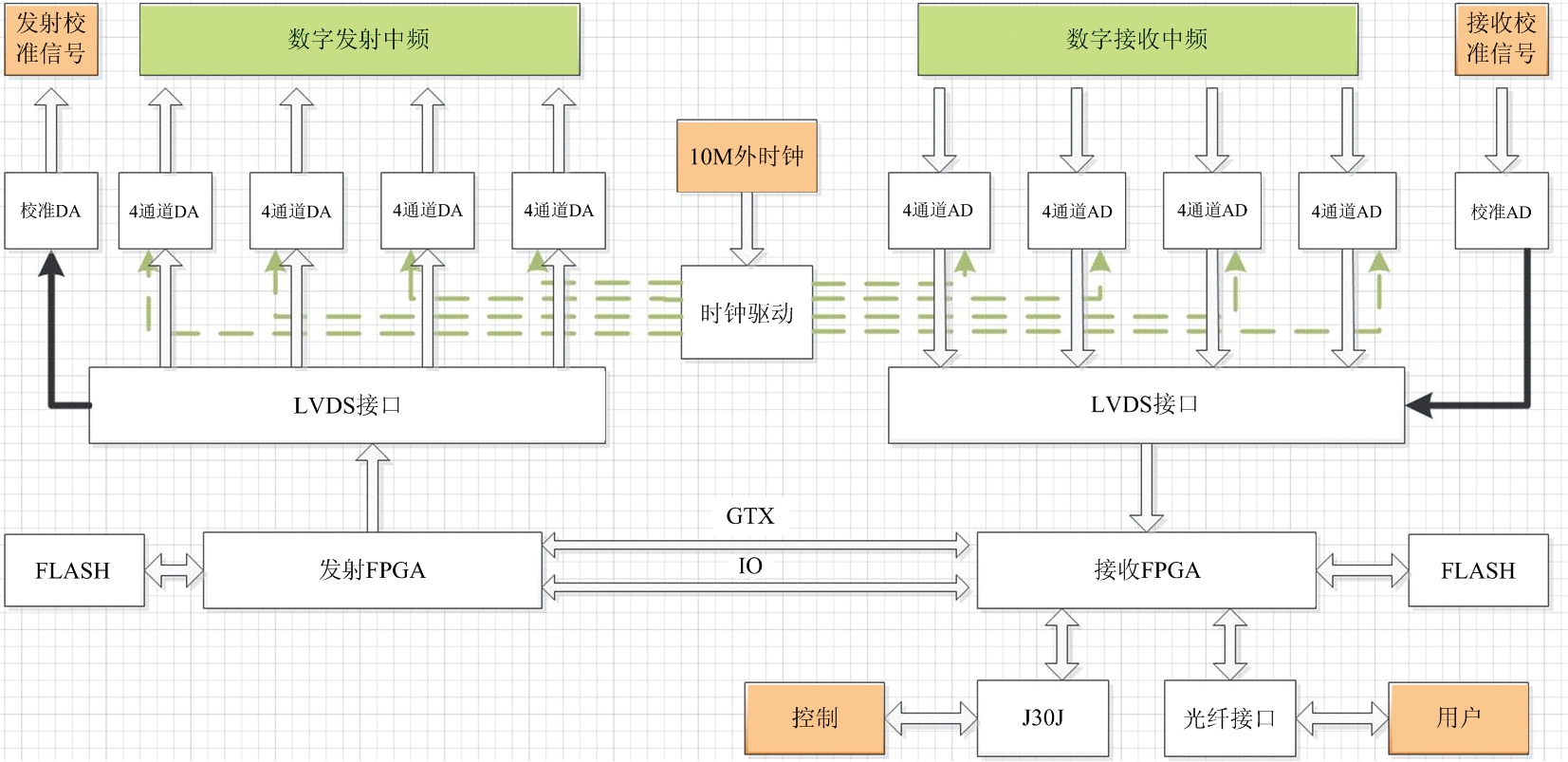

本文将数字中频划分为一块单独的信号处理板,由2片FPGA、4片高速四通道AD、4片高速四通道DA、1片校准AD、1片校准DA、1个低抖动的时钟驱动器和2片SPI FLASH组成。其中2片FPGA之间连接一条高速总线,用来接收用户的高速基带IQ数据。对外的接口都由FPGA引出,包含2片FPGA的配置JTAG组成的菊花链、对外通信的一组高速光纤口和一组低速J30J接口。数字中频处理板的原理框图如图11所示。

在进行波束形成前,需要对每个通道固有的幅度相位差进行校准,常采用乘法器,其实现和原理比较简单,这里重点阐述相位的均衡算法。针对宽带信号,为了避免在中心频点移相带来的孔径渡越效应,最常用的方式均衡方式是分数延时滤波器[10]。分数延时滤波的理想冲击响应为

h(n)=sinc(n-D)

(2)

图11 数字中频处理板原理框图

式中,D=Z+d,Z为整数延时,d为分数延时。

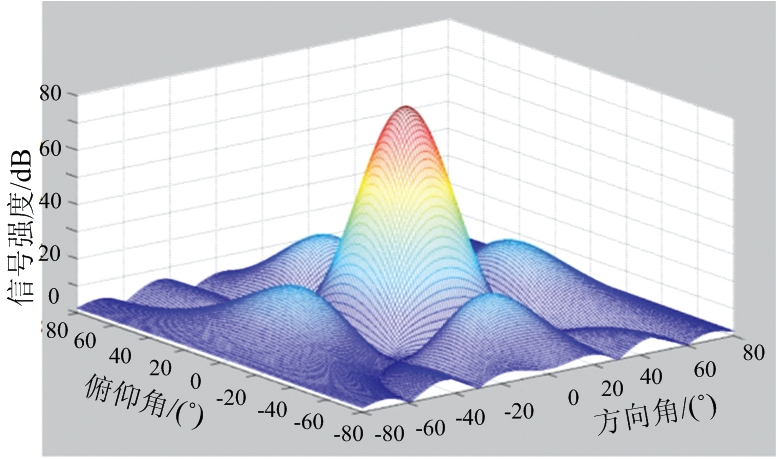

对整数延时,在逻辑器件里面实现起来非常简单。对于分数延时,本文采用FIR滤波器的方式实现。预先在FPGA的内部ROM里生成延时量从0.1*T_data到0.9*T_data的FIR滤波器系数,其中T_data为抽取之后的采样率。每次上电之后,校准网络通过开关切换的方式将校准信号发送至各个射频通道,经过数字信号处理得到各个通道的延时误差,并通过动态加载的方式调用不同的FIR滤波器系数生成相应延时的FIR滤波器,对各通道进行均衡。图12为均衡后的二维波束方向图。

图12 均衡后的二维波束方向图

5 测试与校准

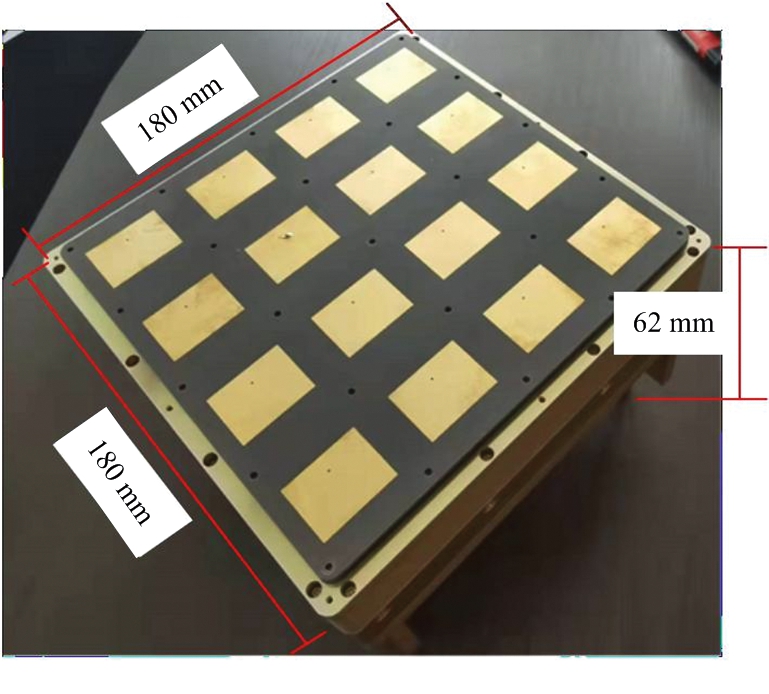

基于以上方案,研制了1套瓦片式集成16通道数字相控阵天线。与传统的C波段砖块式数字相控阵相比,该瓦片式数字相控阵体积减半、重量大幅降低,系统有很好的扩展能力,可以此为子阵进行拼接,组成更大规模阵列。16通道数字相控阵天线的实物如图13所示。

图13 16通道数字相控阵系统实物图

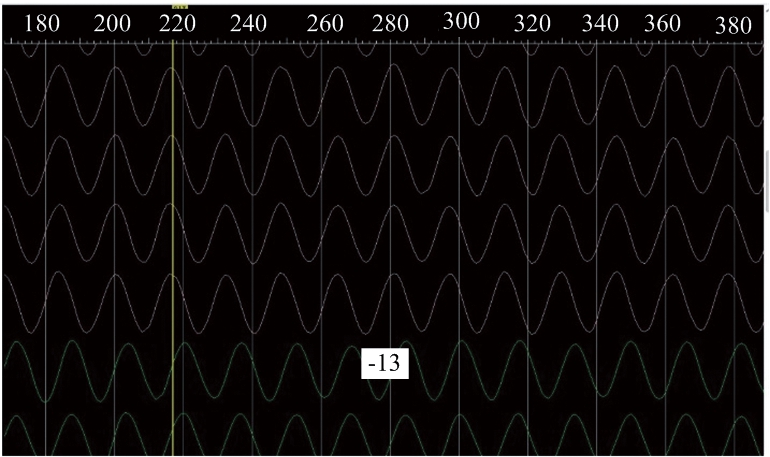

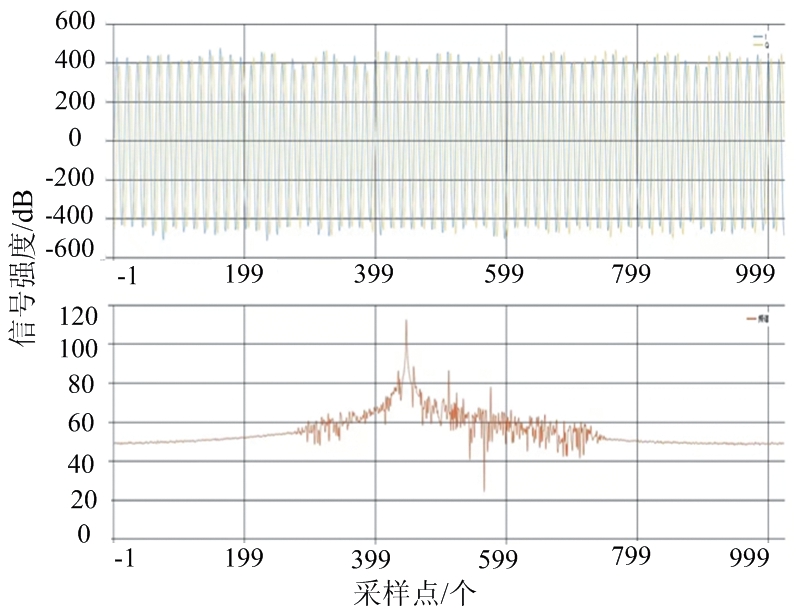

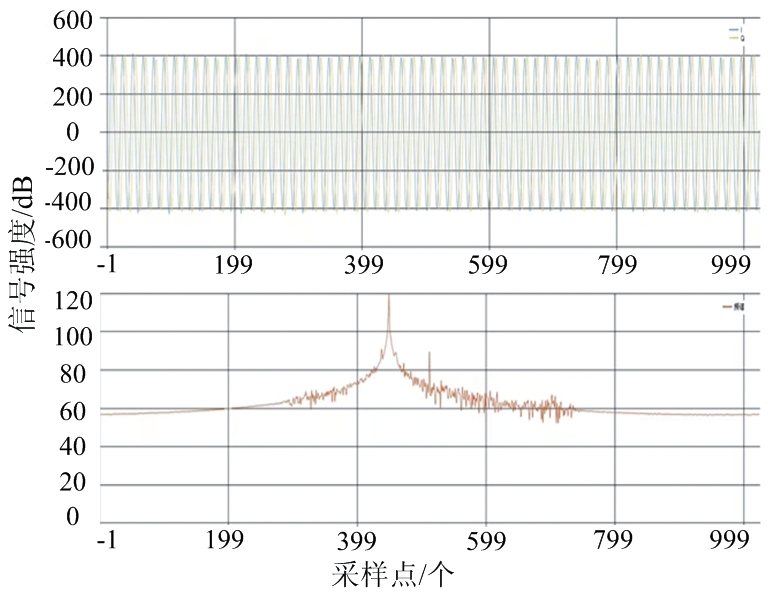

利用远场方式对包含天线单元在内的多通道的幅度和相位不一致性进行校准,校准之前的各通道采样信号如图14所示,各路通道之间存在明显的相位不一致,多通道信号合成效果如图15所示。

图14 校准之前各路通道采样信号

图15 多通道信号合成效果(对齐之前)

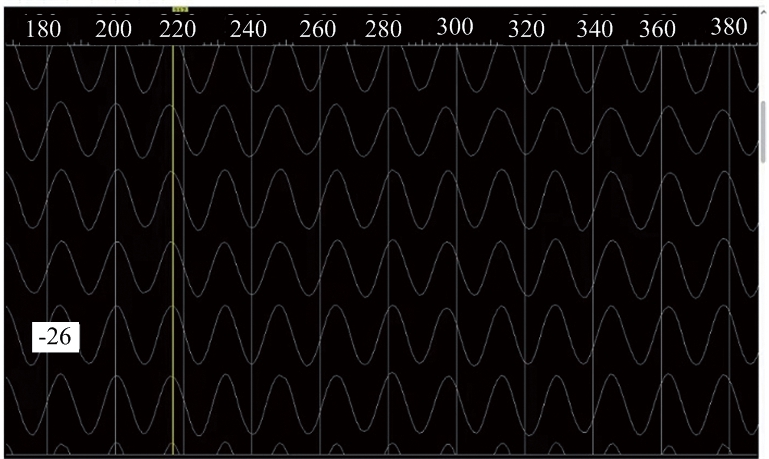

加载数字校准模块之后,各通道的相位对齐情况如图16所示,可见各通道的信号相位完全对齐,多通道信号合成效果如图17所示,信噪比相比相位对齐之前提升3 dB。

图16 校准之后各路通道采样信号

图17 多通道信号合成效果(对齐之后)

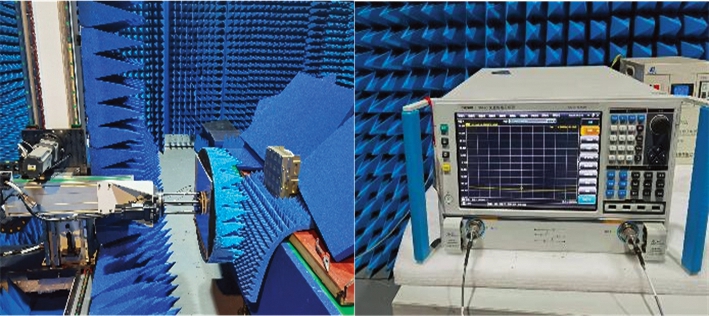

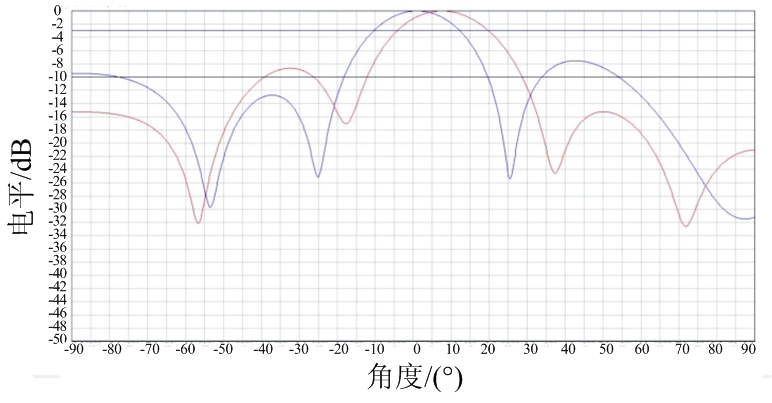

在暗室中对该相控阵天线阵列法向方向图进行测试,测试现场与测试结果如图18和图19所示。由于数字阵架构在通道前段没有耦合检测功能,所以将有源驻波的影响统一到方向图里。

图18 暗室测试现场

图19 数字波束形成方向图(红色:俯仰面,蓝色:方位面)

6 结束语

综上所述,该数字相控阵系统采用瓦片集成方式,包含天线阵面、射频链路、中频链路及数字波束形成基带,经过远场外校准可矫正各通道之间的幅相误差,矫正之后其方向图暗室测试指标与仿真结果接近,可达到数字波束形成的效果。

[1] 张雪莲. 多功能综合射频技术发展研究[J]. 现代雷达, 2020, 42(7):78-81.

[2] 杨跃胜, 傅霖煌. 关于HIC,MCM,SIP封装与SOC的区别及工艺分析[J]. 中国集成电路, 2021, 30(11):65-69.

[3] 徐艳国,李国刚,倪国新.雷达系统未来发展趋势探析[J].中国电子科学院学报, 2013, 8(5):474-480.

[4] 赵晨光.数字相控阵雷达与模拟相控阵雷达性能对比浅析[J].电子技术与软件工程, 2014(6):69.

[5] 吴曼青,葛家龙.数字阵列合成孔径雷达[J].雷达科学与技术, 2009, 7(1):1-9.

[6] 李归,巫书航,张鹏,等.一种宽带单元数字化有源相控阵发射多波束时延设计[J].现代雷达,2018,40(9):36-39.

[7] GUO Guo,YAN Zhenlin,SUN Zhenzhen,et al. Broadband and Integratable 2 × 2 TWT Amplifier Unit for Millimeter Wave Phased Array Radar[J]. Electronics, 2021, 10(22):2808.

[8] 刘明鑫, 尹亮, 汪学刚,等. 基于射频采样宽带数字阵列雷达波束形成[J]. 雷达科学与技术, 2020, 18(4):394-398.

[9] 张跃平.封装天线技术发展历程回顾[J].中兴通信技术,2017,23(6):41-49.

[10] 李杰,章坚武.智能天线的波束形成法及自适应算法[J].杭州电子工业学院学报,2001(6):1-6.